详说片上网络之六:网络分层模型在片上网络上的实现(下)

0赞书接上文,继续谈谈网络分层模型与片上网络的映射关系,以便各位更好的理解片上网络。

在网络模型中,物理层是信息传输的基础和载体,主要作用是实现信号在物理介质上的可靠传输。而要实现信号在物理介质上的可靠传输就涉及到了信号处理、编码原理、电子技术、电磁场与电磁波等多个领域的知识。这部分知识其实挺庞杂的,可以说通信工程这个专业四年大半时间都在搞懂这个问题。而剩下一小半时间则是在学习网络和交换技术。由于这部分内容涉及太多,在这里就不详细展开了。有兴趣的朋友可以去看看这本书:

数字传输工程(第2版) (美)安德森 著,任品毅,冯兴乐 译product.dangdang.com

对于经典片上网络而言,其传输的是标准CMOS数字信号。因此并不需要有太特殊的信号处理、编码技术以及器件技术。使用普通的CMOS电路就可以完成对于信号的传输。唯一需要考虑的就是在传输过程中由于电路本身的问题、信号的干扰、噪声等问题引入信号错误,因而需要引入纠错编码等容错设计技术。当然,片上网络中引入错误的物理因素和普通的通信网络不同,纠错的方法和传统通信网络有非常大的区别。我们小组在近5年来就是深入分析片上网络和传统通信网络纠错技术的不同,发表了一系列比较高水平的论文。这个问题后面回专门开一期甚至几期来介绍。

而上期说到,一些“新技术”的片上网络使用了类似与光、无线、传输线、电磁耦合等传输方法。在物理介质上就有了新的变化,因此这类片上网络就需要关注物理层,如何用物理载体和信号处理技术。然后结合片上网络的特点做一些特定的网络架构、交换方法之类的。这类技术我研究得比较少,所以我就不详细说了。

经典片上网络一般是从数据链路层开始研究的,而在片上网络中数据链路层是指两个实体之间的数据传送过程。在这个层面已经脱离了“信号”的范畴,而进入了“数据”的范畴。在片上网络中数据链路层是指如何把数据从某个实体(路由器/网络接口)中传送到另外一个实体中。所以主要定义的是两个实体之间的交互过程和定义的信号时序。

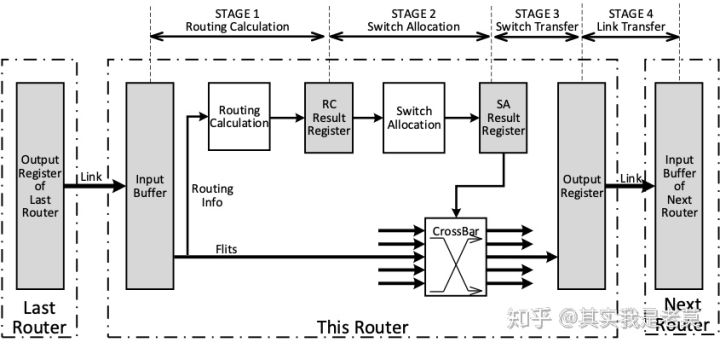

经典路由器的流水级分析

先来看这个图,分成了多个流水级。那么数据链路层对应到哪里呢?对应了从第4级的输出到下一级的输入,这一级被称为Link Transfer。那么就需要定义包传输的数据格式,两个路由器之间的握手信号以及其时序。对于传统的通信网络而言,无论是无线/有线网络,在两个通信实体之间传递信号的延迟比较大。但在经典片上网络中Link上的延迟实际上就是互连线延迟。由于使用片上网络的目的就是“打断”长的互连走线,因此这部分的延迟其实并不突出(在错误注入方面也有类似的现象)。而在这一环节引入延迟最大的因素在于输入缓冲的buffer的写入控制。而片上网络中数据链路层的设计难点,其实也是围绕着输入缓冲的读写控制来展开的。因此在片上网络中的“链路”这一概念是指从输出到输入缓冲这一部分硬件。

正如在网络分层模型中,在数据链路层一般被分为两个子层 :逻辑链路控制(LLC)协议和媒体访问控制(MAC)协议。而对应在片上网络中则分别是对应两个功能:流量控制和链路资源分配。而这一切的根源又在于如何合理的利用好“链路”这一硬件资源。在片上网络中,控制对于链路这一资源的使用是靠“仲裁电路”来实现的。在经典的计算机/通信网络中,链路资源的分配很多时候是依靠“竞争-回退”这一机制来实现的。当年学习N个网络类课程的时候,学了无数的协议。但其实核心的这一点是很久以后才领悟到的。在这一点上看,片上网络沿袭的并非经典的计算机/通信网络的那套机制而是继承了计算机系统内部总线的“请求-仲裁”机制。这其实是因为经典的计算机/通信网络要面临一个“灵活组网”的问题。在网络中需要考虑到新的网络节点/终端加入或者离开网络的情况。这种灵活性在“无线自组织网络”中达到了最高要求。而片上网络则是用于芯片内部互联的,在设计阶段可以有足够多的先验信息来实现定制化。

具体来说,片上网络对于链路控制是依靠Switch Arbiter这样一个仲裁电路来实现的。在很多片上网络的论文里面,路由器的原理图是这样画的:

图1 常见的片上网络路由器原理图

图1是很多论文里都出现的一种介绍片上网络路由器的图。这种图如果不是出现在综述类论文里,一般这个论文就不用怎么看了,对于真正的电路设计的参考意义太小。长期受这种图的“毒害”会产生两个错误印象:1.Crossbar是一个完整的整体,对于路由器的控制主要是“施加”在Crossbar上面的。2.在路由器中Routing Computation 、 VC arbiter、Switch arbiter分别都是一个,通过他们来控制整个路由器的路由以及资源分配。其实这种观念是对于硬件设计是极其错误的。

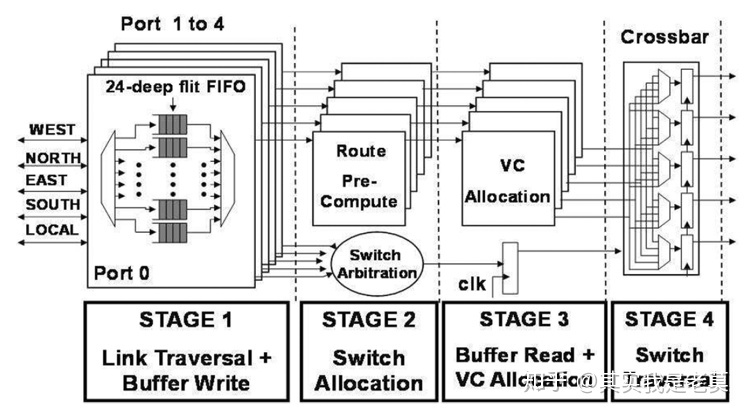

让我们回头来看Intel的这篇经典的论文“SalihundamP , Jain S , Jacob T , et al. A 2 tb/s 64 mesh network for a single-chip cloud computer with dvfsin 45 nm cmos[J]. IEEE Journal of Solid-State Circuits, 2011, 46(4):757-766.”

图2 A 2 tb/s 64 mesh network for a single-chip cloud computer with dvfsin 45 nm cmos中的路由器内部结构示意图

图2所展示的路由器内部结构图就比图1更加接近与真实的硬件电路结构,起码从图中可以看出来Routing Computing、VC Allocation这些控制单元是每个端口上独立有一个。另外也把Crossbar内部给拆开了,是多个多路复用器而已。独立的来看每一个多路复用器与一个输出端口寄存器相连,通过多路复用器来选择到底哪一个输入端口的可以数据可以被存入输入端口。而多路复用器的控制端是和Switch Arbitration的输出连接在一起的。换言之,是由Switch Arbitration的结果来断定哪个输入端口有权使用当前的输出端口。从图2可以看出多个输入端口有信号线与Switch Arbitration连接,通过“请求-仲裁”的模式来分配输出端口的使用权。而分配了输出端口的使用权,实际上也分配了整个从输出到下一个路由器输入端口的“链路”的使用权。当然,这个图比较不好的一点是没有表现出来实际上witch Arbitration也是有多个的。一个输出端口一个,对链路的使用权独立的仲裁。

如果单看Switch Arbitration这一块,把问题说的比较清楚的是MPSoC领域宗师级人物Luca Benini小组发的一篇论文“M. Kakoee, V. Bertacco, and L. Benini, “At-speed distributedfunctional testing to detect logic and delay faults in nocs,” IEEETransactions on Computers, vol. 63, no. 3, pp. 703–717, 2014.”:

图3 MPSoC一代宗师Luca Benini的论文中给出的控制通路和数据通路的示意图

请大家看看图3,请透过这张用word制作出来的简陋图片朴素外表下体验直击灵魂的震撼。这张图深刻的反应了片上网络路由器中输入端口和输出端口之间、控制通路和数据通路之间的交互关系。真正的大师,是不屑于用华丽的图片来装饰自己的论文(Luca Benini组很多论文的配图都惨不忍睹,但最近几年有所改善)。输入端口(图中为West端口)通过RC(Routing Computing)来计算被存储在输入缓冲器里的包要发往哪个输出端口,计算完毕以后向对应端口(图中为East 端口)的East Arbiter发出请求信号。East Arbiter根据当前的请求信号,判定到底哪个输入端口有权使用East端口把数据包发出去。从而通过自身的输出作为East Output Mux的选择端控制信号,来选择到底哪个输入端口的数据可以被存到输出寄存器中。这里仅仅以了一组输入到输出的通路为例,其它的通路其实都按照类似的模式工作。当然,East Arbiter的输出还会作为一个反馈信号给到输入端口的控制状态机。

这篇论文绝对是一篇值得所有有志于研究片上网络的同学仔细阅读的论文。当年我看到这篇论文以后有一种醍醐灌顶,瞬间被打通了任督二脉的感觉。这篇论文对我有两点颠覆性的作用:首先,我在头脑中真正的形成了片上网络路由器硬件结构的概念,此前由于受通信网络影响太深,一直想不清楚片上网络硬件应该是怎么样的;其次,我发现了这篇论文一个不足,而恰恰我那时候的研究已经进入到死胡同,但如果将我们当时提的路由算法反用到这篇论文提到的测试/可测性设计场景中,却又柳暗花明又一村。于是,从那时起,我就误打误撞的进入到了可靠性/可测性设计这个领域,并且形成了近年来我看家的学术研究方向。

前面絮絮叨叨的讲了这么多,就是讲了一个数据链路层中的介质访问控制如何对应到片上网络中。而数据链路层还有逻辑链路控制的功能,包括了传输可靠性保障和控制、 数据包的分段与重组、 数据包的顺序传输。在片上网络中这三点其实都有所实现,但核心是控制包的传送过程,确保数据包在链路阻塞的时候不会被继续传送而导致数据/控制错误等。这个问题是依靠在路由器之间传递握手信号/信令来实现的。同时在片上网络中的数据包也存在分段传送的控制问题。但这部分的内容比较复杂,涉及到很多协议和电路协同设计的思想。而在具体设计协议的时候,又大量参考了并行计算机内部互联网络的一些设计思想。所以这部分内容很多,完全可以单开一讲来说。今天就先不谈了。

那么网络层的功能在片上网络上映射就简单多了。网络层主要做的作用是“寻路”,也就是确定数据包应该发往哪个输出端口。继续从图3可以看出,网络层的功能其实就是通过一个叫RC(Routing Computing)的硬件单元就可以实现。这个硬件单元根据数据包中所包含的一些信息(通常存子啊包头里),根据路由规则/算法计算得出接下来的数据包需要发往。和计算机网络/通信网络不同,由于片上网络的结构相对固定且对于资源消耗敏感。因此并不适用于过于复杂和自适应的路由规则/算法。片上网络的路由规则/算法一般要求可以写成逻辑表达式和基本的算术运算的组合。

当RC按照路由规则计算出包要往哪里发以后,会产生一个请求信号送到对应的输出端口的Switch Arbiter中。后面的过程上面已经说过一遍了,在这里就不重复了。

由于网络层或者说路由算法仅仅和片上网络的一个功能模块对应,因此成为“研究人员”尤其是是新手研究人员的“最爱”。在如果有一个成熟的片上网络仿真器,那么如果研究网络层或者说路由就只需要修改RC这一个模块所对应的规则。而路由规则嘛,是可以根据不同情况相出各种各样的花样的。所以很多新手研究人员对此“乐此不疲”,但很多研究几乎没有实际的价值。

最后就到了传输层,传输层的目的是保证数据端到端的可靠传输。在片上网络中传输层是依靠片上网络接口和及其驱动程序来完成的。从主机这一侧看过去,完成了对于某一个特定接口的访问和读写。网络接口将整个片上网络抽象为了一个面向本地总线的特定接口,而驱动程序则是完成了对于这个接口的读写过程。

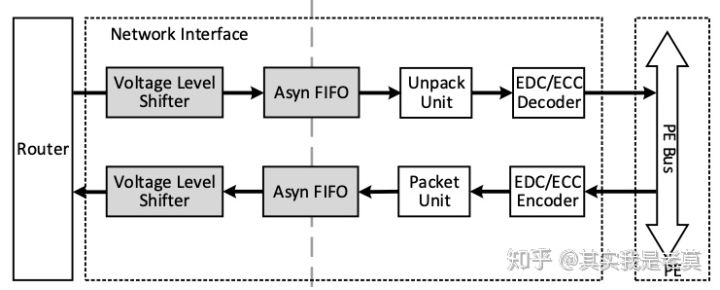

一个片上网络接口的基本抽象如下图所示:

图4 片上网络接口功能示意图

从图4可以看出,片上网络从处理单元(PE)这一侧看过去,是通过总线对一个特定的接口访问。依次经过编码、数据打包、异步FIFO缓存、电压变换被传送到便片上网络路由器中。接收的过程是一个逆过程。以异步FIFO为界,可以把片上网络和PE划分成不同的电压域。

在基本的片上网络接口上,主要依靠软件来实现传输层的各项功能。而如果考虑要设计功能更强大的网络接口,也可以考虑把纠错、重传、流量控制等功能做成专门的电路模块放在网络接口里。

继续再往上就是会话层、表示层和应用层,其实都已经脱离了片上网络研究的范畴,本质上已经是在PE上运行的软件。

用一幅图来归纳一下一下片上网络和网络模型的对应关系:

图5 本小组在ISCAS2017上口头报告PPT中的一张示意图

图5是我们在ISCAS2017上做口头报告的用的一张图解释片上网络与网络模型之间的对应关系。大家可以对照着再回顾本文慢慢体会。这个图是报道了我们当时设计的一种具备“跨层设计”思想的片上网络纠错电路。以后有机会我们再来详细介绍一下这篇论文。顺便说一下,我们这个方向研究的论文的图和设计思想多次被“擦边抄袭”和过度引用。犯事都是南亚某大国的大学,在此对他们表示强烈的鄙视。

最后,提几个片上网络的特点。

1.数据链路层是片上网络的基础,链路相关的电路设计和链路资源是片上网络的基础。

2.在片上网络中,链路资源本身(互连线、输入缓冲、交换矩阵用的多路复用器)以及针对链路资源的控制电路(Switch Arbiter)占了片上网络路由器的主要面积。

3.链路资源的分配,依靠的是“请求-仲裁”的方式。因此片上网络路由器本质上应该分为输入和输出两个部分。链路资源的分配过程其实是由不同的输入在竞争输出。

4.网络层的功能就是对应到片上网络路由器中的一个路由计算单元,主要的目的是计算保存在输入缓冲中的包应该从哪个输出端口被送出去。

5.传输层的功能在片上网络中是由片上网络接口和与之匹配的驱动软件共同承担的。

从以上的总结可以看出,片上网络虽然和网络模型之间有对应关系,但是有自己的特点。后面我们会对此来做详细分析,并介绍我们如何抓住这些特点做出了自己的研究工作的。