多端口(大于8)RAM设计

0赞体外话:

一直以来我写的东西对新手理解不是很友好,嗯,因为那些语法,状态机,时钟,时序 等等东西别人写的比我好多了,而且我也没兴趣。我这里没有“7天学会FPGA”,而且几乎让人绝望,如果没有人执导,可能“7年也不一定学会”(我认为的学会,不单是语法),我自己也不是一两年就学会的,从我接触第一具体的工程项目(不是从verilog语法学习算起哦,语法书完完整整地我看来3遍,花了半年)到我能独立开发一个项目花了3年+的时间!!!。这六年来到现在隐隐约约的觉得FPGA可以往某方面发展(我更习惯用“进化”)。我说的这些东西在网上几乎找不到类似的,比如NoC(Net on Chip)网上很难找到一个具体的实现和应用。我的文章可以找到Noc的一种有效的(我在工程上已经使用,具体代码涉及机密,不能公开,实现方式可以说说),本文也是NoC的一种简单的应用场景。

在写《一种神经网络的FPGA实现》前写下这篇,做一个技术铺垫,免得思维曲线太陡。

资源:

1、单口RAM(当然可以用双口RAM,简单起见用单口讲解),读写都是同一口,通过WEN信号区分(和xilinx的一样),读数据输出延时2个clock。

2、Interface D,接口(systemverilog)。就先叫接口D吧,接口只包含3个信号,valid,ready,data[DSIZE-1:0]。valid,data[DSIZE-1:0]是上游(master)输出给下游(slaver)的,ready是下游(slaver)输出给上游(master)。只有当valid和ready都有效时传输才是有效的。这个可以参考AXI4的valid ready时序(很简单)。这个很重要,我的文章所提到的接口时序都是按这个来的。

需求:

1、8个写端口,8个读端口。(其实是没有限制的)

约束及特点:

1、不会采用DMA的方式,因为DMA的方式对于读来说,从发起到完成,期间需要等待slaver返回数据,才能完成单次操作,会复杂化和影响吞吐。(当然在其中插入Cache实现可以稍微解决,但是会更复杂,资源消耗也会增加)

2、采用全流水方式,读输出时 数据是和地址打包的,数据流调度控制完全通过接口的valid和ready来自动控制, 所以读写完成都不会有固定周期完成,只会在某个延时区间内,区间的范围又端口的数量间接决定(如果只用一层M2S,S2M,这个区间就不会和端口数量有关)

3、个个端口间没有读写互,谁先谁执行

实现关键点:

1、interconnect M2S,S2M 多口到单口,单口到多口的实现方式,我上一篇文也有提到。

2、仲裁,这个仲裁其实就是M2S里面的,这个很重要必须单独摘出来讲。

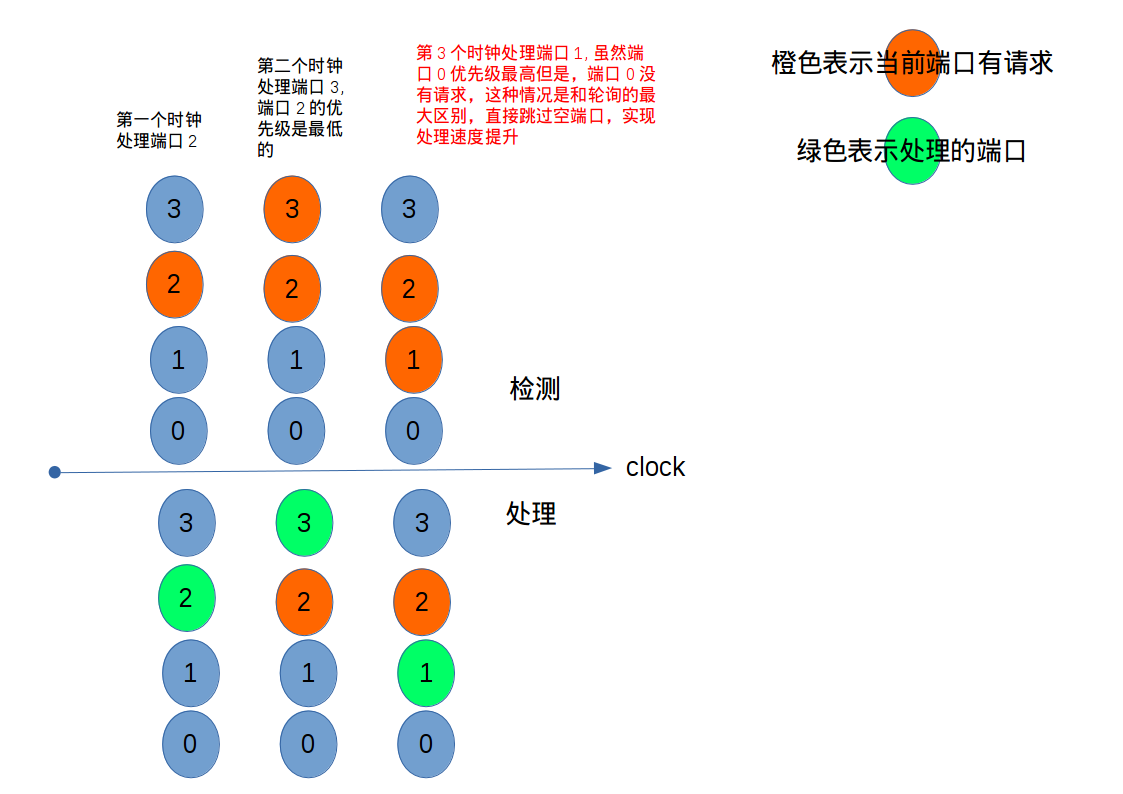

这个仲裁器必须实现优先级轮询,注意不是普通的轮询,比如有端口 0,1,2,3。如果第一次处理端口1,那么下一次3的优先级是最高的,0次之,依次递减。

3、Combin模块,把读的地址延时两个周期后与读出的数据合并输出,功能是很简单,如果只有valid+data是很简单,加上ready信号后,其实比轮询还难,表面上看简单而已。

应用:

用于NoC,多并发RAM操作

--@--Young--@--