PCIe扫盲——Lattice ECP3/ECP5 SerDes简介

0赞连载目录篇:http://blog.chinaaet.com/justlxy/p/5100053481

FPGA发展到今天,SerDes (Serializer - Deserializer) 基本上是标配了。从PCI到PCI Express,从ATA到SATA,从并行ADC接口到JESD204,从RIO到Serial RIO,……等等,都是在借助SerDes来提高性能。SerDes是非常复杂的数模混合设计,用户手册的内容只是描述了森林里面的一棵小树,并不能够解释SerDes是怎么工作的。而本文也主要是基于Lattice ECP3和ECP5 的SerDes UG,来简单地介绍一下Lattice ECP3&ECP5 SerDes的一些基本特性。如需深入了解SerDes,可以参考一下我之前转发的博客:SerDes扫盲:http://blog.chinaaet.com/justlxy/p/5100052786 ,以及本文附件中的硕博论文。亦或者是到IEEE Xplore下载相关论文资料。

废话不多说,进入正题。

Lattice的ECP3/ECP5系列FPGA内部集成了SerDes/PCS的硬核(Hard Core),其速率最高可达3.2Gbps,而ECP5-5G系列的SerDes最高可达5Gbps。Lattice的SerDes是基于CML信号的,借助 PCS(物理编码子层,Physical Coding Sublayer)可以支持PCI Express、JESD204A/B、SD-SDI、HD-SDI、3G-SDI、GbE、CPRI、Gigabit Ethernet (1GbE and SGMII)和XAUI等多种串行通信协议,具体如下图所示。

就PCIe(PCI Express)而言,ECP3/ECP5可支持1.0/1.1版本(2.5Gbps),而ECP5-5G还可支持2.0版本(5Gbps)。借助Lattice提供的PCIe相关的IP(Endpoint&Root),可以快速的完成基于FPGA的PCIe设备的开发。

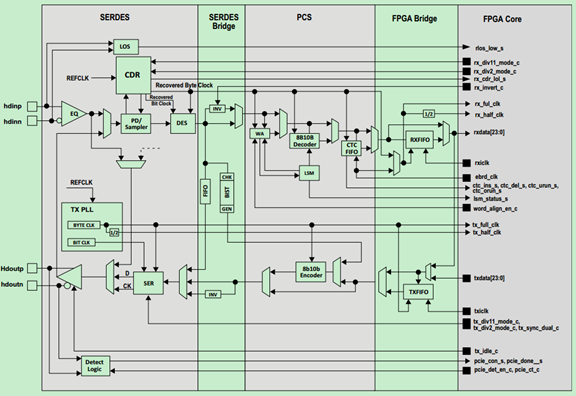

Lattice ECP3,ECP5(ECP5-5G)的SerDes/PCS结构基本相同,区别主要在于ECP5将两个SerDes/PCS通道合并到一个叫做DCU的模块中去。ECP5的每一个DCU均包含一个AUX通道(以及TxPLL),而ECP3每四个SerDes/PCS通道才包含一个AUX通道。ECP3和ECP5的结构图分别如下图所示:

其中,ECP5的SerDes/PCS的单个通道的详细结构图如下图所示:

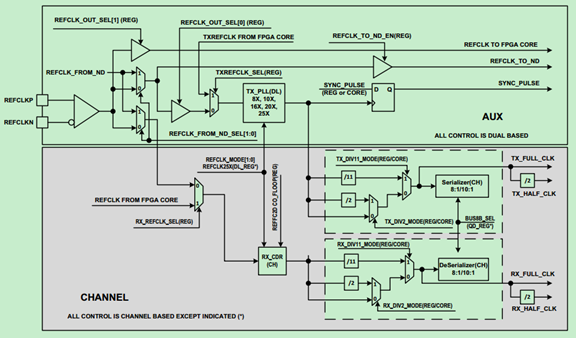

ECP5的SerDes时钟结构图如下:

注:本文只是对Lattice ECP3/ECP5器件中的SerDes/PCS进行了简要的介绍,具体还请阅读参考阅读中的相关UG。

参考阅读:

1、Lattice ECP3 SerDes/PCS User Guide:

![]() LatticeECP3SerdesPCS UsageGuide.pdf

LatticeECP3SerdesPCS UsageGuide.pdf

2、Lattice ECP5/ECP5-5G SerDes/PCS User Guide:

![]() ECP5 and ECP5-5G SERDESPCS Usage Guide.pdf

ECP5 and ECP5-5G SERDESPCS Usage Guide.pdf

3、10Gbps-SerDes中的高速接口设计:

4、高速SERDES接口芯片设计关键技术研究: