Lattice FPGA 7:1 LVDS 接口

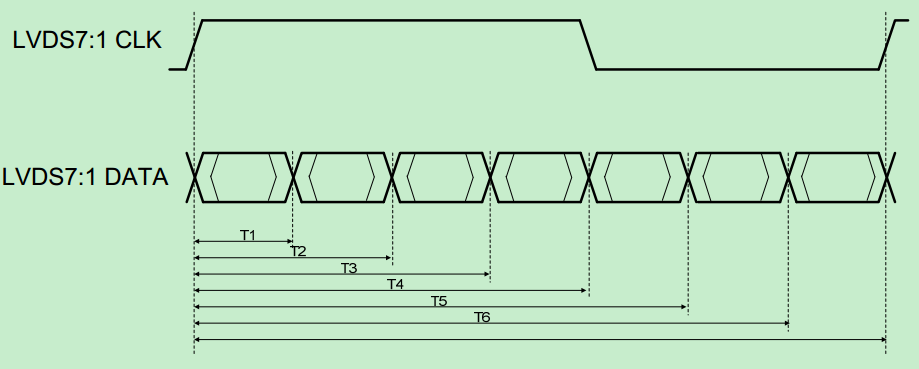

1赞包括多个数据位和时钟的源同步接口已经成为电子系统中移动图像数据的常用方法。一个通用的标准是7:1 LVDS接口(用于通道连接,扁平电缆连接和摄像机连接),这已成为许多电子产品,包括消费电子设备、工业控制、医疗,汽车远程信息处理中的通用标准。如Sony的ECX337 OLED采用的就是7:1 LVDS的接口。7:1 LVDS信号示意图如下:

图1. LVDS7:1时钟数据对应示意图

Lattice的ECP5/XO2/XO3/CrossLink等器件都支持7:1 LVDS的Hard Core接口。而早期的器件(ECP3/ECP2/XP2等)则可以通过GDDRX2加上4:7的逻辑来实现LVDS7:1接口。

ECP5/XO2/XO3/CrossLink的7:1 LVDS是基于Generic DDR71接口,并借助相关的同步逻辑和时钟分频逻辑实现。接收端的接口要稍微复杂一点,在发送端的基础上,还需要一个PLL和字同步逻辑。

1、ECP5/XO2/XO3/CrossLink 7:1 LVDS发送端结构

ECP5/XO2/XO3/CrossLink7:1 LVDS发送端结构如下图所示,

图2. ECP5/XO2/XO3/CrossLink 7:1发送端结构示意图

其中ECLK是SCLK频率的3.5倍,REFCLK与ECLK频率相同,CLKOUT是ECLK的3.5分频。以REFCLK为141.75MHz为例,则ECLK为141.75MHz,SCLK和CLKOUT为40.5MHz。单条数据Lane的速率为:ECLK*2=141.75M*2=283.5Mbps。(注,乘2,是因为DDR)

需要注意的是SCLK只能走主时钟网络(Primary Nets)。

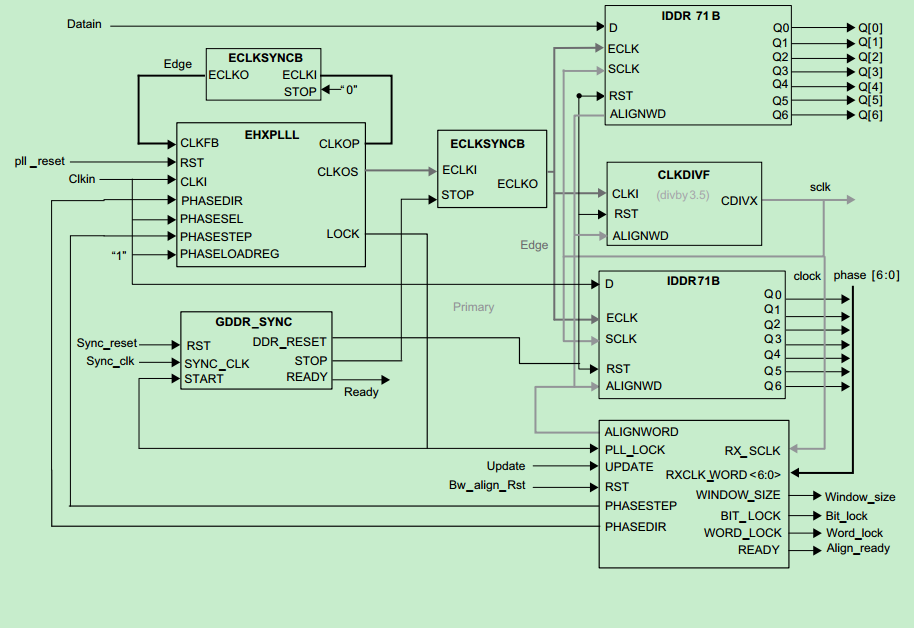

2、ECP5/XO2/XO3/CrossLink 7:1 LVDS接收端结构

ECP5/XO2/XO3/CrossLink 7:1 LVDS接收端结构如下图所示:

图3. ECP5 7:1接收端示意图

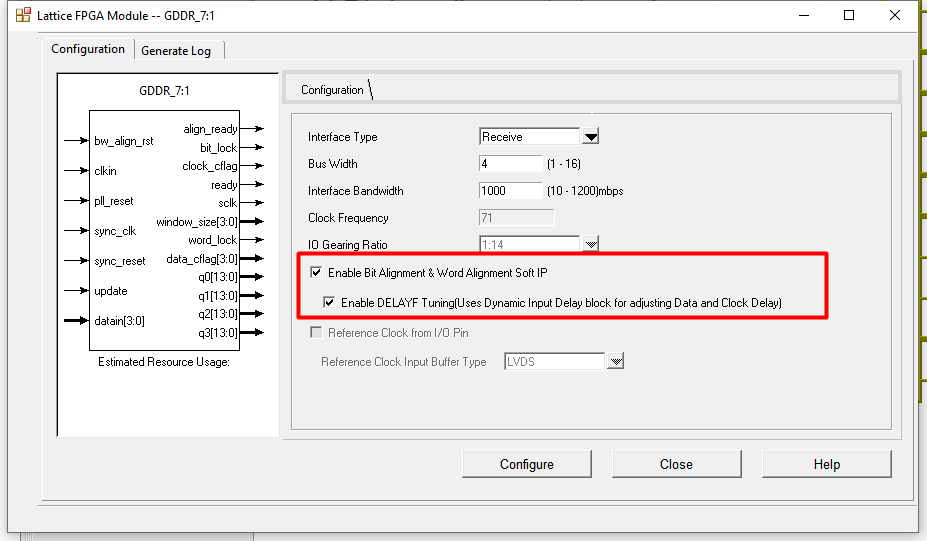

其中,XO2/XO3的GDDR71 module在配置的时候不会自动生成对齐和同步逻辑,这部分需要用户自行设计。用户可以参考RD1093中的相关源码完成设计。ECP5和CrossLink可以在Clarity的配置界面选择是否要自动生成这些逻辑。CrossLink还可以选择是否使能额外的DELAYF模块(用于支持高速场景下的应用),如下图所示。

图4. CrossLink GDDR71的配置界面

此外,CrossLink还提供了FPD-Link Rx/Tx、DSI to FPD-Link和FPD-Link to DSI等IP可用。

主要参考资料:

1、FPD-Link(LVDS7:1)与FPD-Link II&III介绍:http://blog.chinaaet.com/justlxy/p/5100063850

2、Lattice ECP5/XO2/XO3/CrossLink High-Speed IO UG

3、RD1093. MachXO2,MachXO3 and ECP5 7:1 LVDS Video Interface

4、RD1030. LatticeECP3,LatticeECP2/M and LatticeXP2 7:1 LVDS Video Interface

5、FPGA-IPUG-02021. OpenLDI/FPD-LINK/LVDS Receiver Interface IP

6、FPGA-IPUG-02022. OpenLDI/FPD-LINK/LVDS Transmitter Interface IP