PCIe扫盲——关于PCIe参考时钟的讨论

5赞连载目录篇:http://blog.chinaaet.com/justlxy/p/5100061871

本文来聊一聊PCIe系统中的参考时钟,主要参考资料为PCIe Base Spec和CEM Spec。在1.0a和1.1版本的PCIe Base Spec中并没有详细的关于参考时钟的描述,而是在与之对应的CEM Spec中提及。从V2.0版的PCIe Base Spec开始,在物理层电气子层章节中增加了参考时钟相关的内容,同时提出了PCIe参考时钟的三种架构:

1、Common Refclk (Shared Refclk) Architecture

2、Data Clocked Rx Architecture

3、Separate Refclk Architecture

以及扩频时钟(Spread Spectrum Clocking,SSC),时钟测试测量等内容。

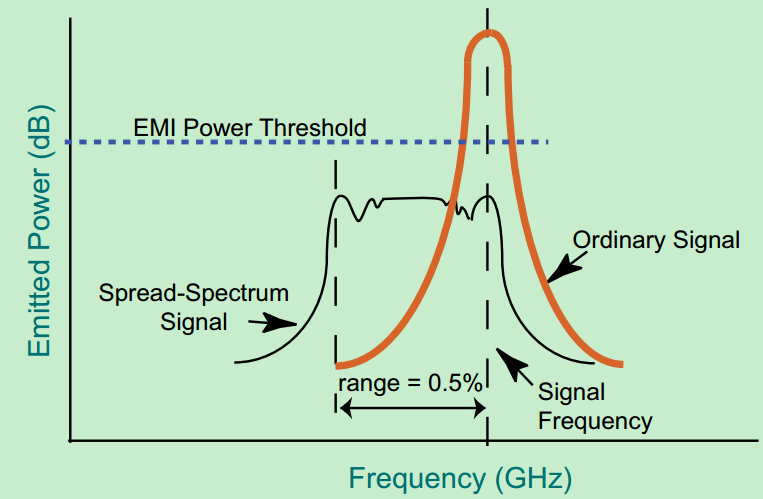

关于扩频时钟,可以参考之前的文章:http://blog.chinaaet.com/justlxy/p/5100064134。扩频时钟对于PCIe来说是可选的,并非是强制的。如果选择支持扩频时钟的话,需满足以下要求:

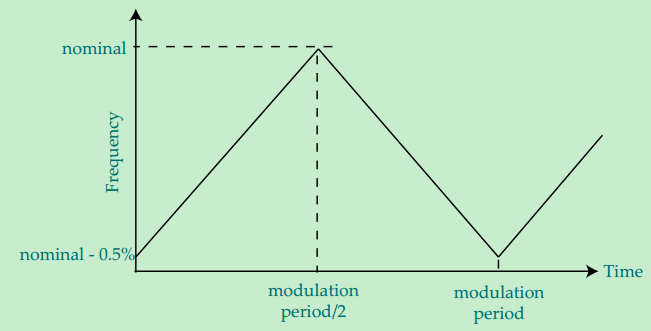

※ 调制范围为+0%到-0.5%,即向下扩频(Down Spreading),如下图所示

※ 调制频率必须在30KHz到33KHz,一般为三角波

※ 参考时钟源的抖动(Jitter)需在300ppm以内

带有SSC的参考时钟频率变化曲线如下图所示:

注:为什么选用的是向下扩频,而不是中心扩频或者向上扩频?主要是考虑到,当100MHz已经是系统最靠基准频率的话,向上扩频或者中心扩频会导致系统基准频率超过最高值,进而可能引发系统工作异常。

注:三角波的能力较为集中在低次谐波中,相比于正弦波,方波或者锯齿波,更适合用于SSC中。

关于参考时钟详细参数需求,已经测试测量等相关内容,本文将不会涉及,具体请参考PCIe CEM Spec和2.0或以上版本的PCIe Base Spec中的相关章节。

下面,我们来简单地聊一聊前面说到的三种参考时钟架构,首先是

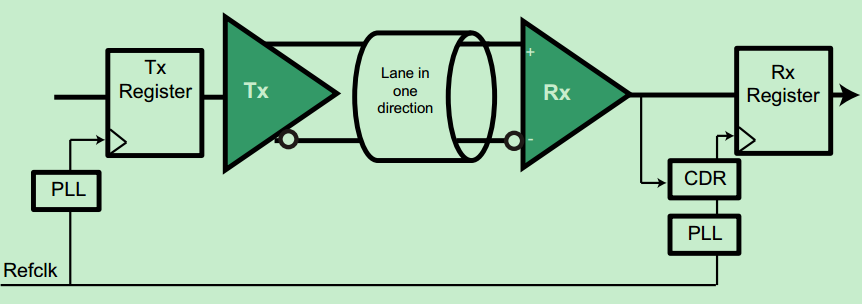

Common Refclk (Shared Refclk) Architecture

Common Refclk (Shared Refclk) Architecture的示意图如下图所示,

这种参考时钟架构是Spec推荐使用的,链路两端的器件均使用同一个参考时钟源。即使系统使用了带有扩频的参考时钟源,时钟抖动也只有-300~+2800ppm,这对于物理层中的RxCDR和TxPLL就比较友好了,可以降低RxCDR和TxPLL的复杂程度,达到节约成本的目的。其次,当PCIe链路处于L0s或者L1状态时,即使链路上没有数据流,RxCDR依然可以设计出保持锁定的状态,这样做的好处是,链路从L0s或L1状态恢复到L0状态的时间将会更短。

Data Clocked Rx Architecture

Data Clocked Rx Architecture的示意图如下图所示:

从示意图来看,这种参考时钟架构最为简洁,Rx端器件的CDR并不需要参考时钟,而是直接从数据流中恢复出时钟。不过这种结构的RxCDR几乎很少在FPGA的SerDes中使用,因为在没有外部参考时钟的协助下,CDR实现锁定都是一个很大的挑战,还要保证在5600ppm的抖动范围内不失锁(对于带有扩频时钟的PCIe链路来说)。

注:绝大部分的FPGA SerDes都是多协议SerDes,除了支持PCIe外,往往还需要支持其他主流的串行协议,比如SATA、USB、DisplayPort、HDMI、Ethernet (Q)SGMII、CoaXpress、CPRI、FPD-Link II/III、Serial RapidIO、SLVS-EC等等。这种参考时钟架构对于PCIe来说行得通,对于其他的某些串行协议来说可能是无法实现的。

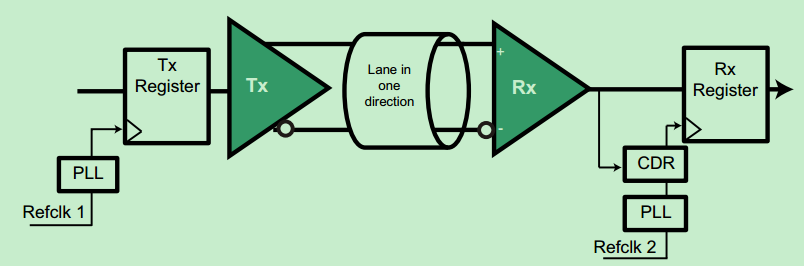

Separate Refclk Architecture

Separate Refclk Architecture的示意图如下图所示:

PCIe Spec强烈不推荐使用这种参考时钟架构,尽管这是其提出的三种参考时钟架构之一。PCIe Spec强调,如果使用这种架构,扩频时钟必须被禁止使用(2.5GT/s & 5GT/s),因为这中情况下使用扩频时钟的话,CDR的带宽需甚至需要大于5600ppm,这对于CDR来说是非常大的挑战。

需要注意的是,PCIe Base Spec V3.x中,提到对于8GT/s的PCIe链路而言,在Separate Refclk Architecture下实现扩频时钟也是可行的(即Separate Refclk With Independent SSC (SRIS) Architecture),但是需要更复杂的CDR设计,具体请参考Spec相关章节。