几个处理器软核在FPGA上的使用

0赞正是因为FPGA的灵活性,我们也可以在上面构建CPU,总线,各种外设等。几个开源组织上的8032/8051核,如MC8051、OpenCores组织的OC8051、DesignWare提供的DW8051等,这些8051IP核都优化了结构,比传统的Intel MCS51有更好的性能,在不同工艺的FPGA上面可以跑在不同的时钟频率,具体可以看IP核的文档中有综合时序报告。当然,也有一些与主流的微控制器兼容的CPU核,比如OpenMSP430,与AVR兼容的8位机等。

当然也有一些性能比较强的32位处理器如OpenRISC1200、Nios II、MP32等等。这几个处理器在性能表现与FPGA的工艺有很大的关系,有些ASIC中甚至会使用这类IP核流片。一般说来,性能介于ARM7和ARM9之间。因为Altera有一个较为完善的系统级总线互联结构设计工具Qsys,所以很方便构建Nios II的基本系统。

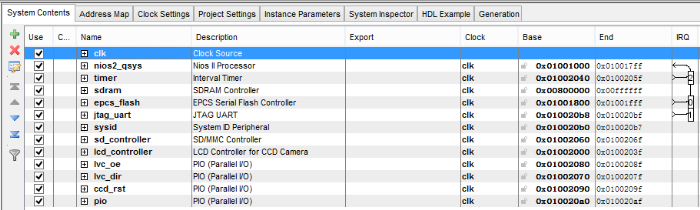

下面是一个我构建的一个Nios II的系统:

上图中有Altera提供的Nios II CPU核,定时器Timer,SDRAM控制器,EPCS Flash控制器、PIO等等。通过Qsys,我们可以自定义所需的外设,只要按照Altera的Avalon总线标准定义端口,通过设置即可与Avalon总线互联,具体可以参照Altera的相关文档。其中的SD卡控制器和TFT LCD(8080接口)控制器就是我自己定义的。然后给外设分配地址和中断向量号,生成后即可综合。通过Nios II SBT进行基于Nios II处理器的软件开发,调试。

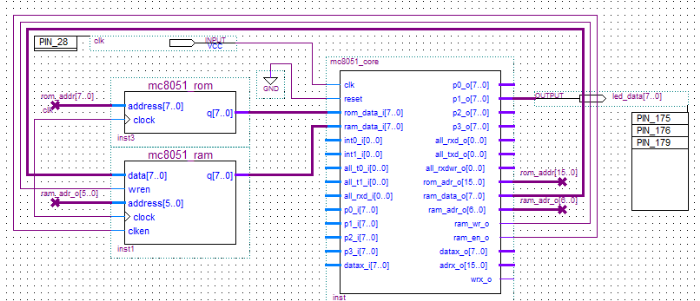

下面是基于MC8051构建的系统:(原理图符号形式)

由于其指令几乎与传统8051完全兼容,所以只要硬件一致的配置即可直接在Keil中开发。如果对其中部分有所精简,可以按照具体的结构自己定义一个头文件进行使用。DW8051对于经典8051系列MCU的外部RAM接口是使用wishbone总线描述的,所以可以方便的进行外设的扩展。

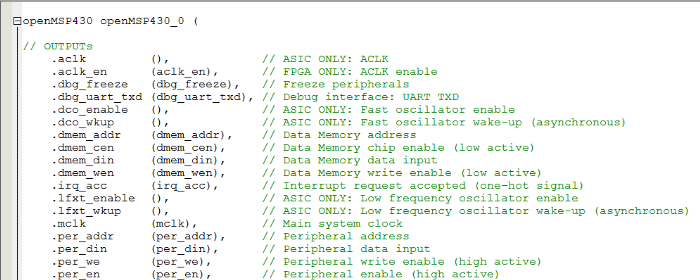

下面是OpenMSP430的基本系统(RTL代码):

软件部分可以使用mspgcc等开发。

总之,基于软核的系统可以在FPGA平台上灵活的使用,但是,前面说过,目前来说还不会有大量的应用。不过,这不等于说学习它没有用,如果想要应用好他们,只要需要很好的硬件(数字电路、微处理器)和软件开发(汇编语言、C语言)基础。通过它们可以更深入理解MCU甚至SoC系统的底层硬件逻辑,对嵌入式系统的开发大有帮助。