单比特信号跨时钟域处理

0赞单比特信号跨时钟域处理:clock domain crossing

亚稳态:指触发器无法在某个规定时间段内达到一个可确认的状态。

一般解决方法:

1 降低系统时钟

2 用反应更快的FF

3 引入同步机制,防止亚稳态传播

4 改善时钟质量,用边沿变化快速的时钟信号

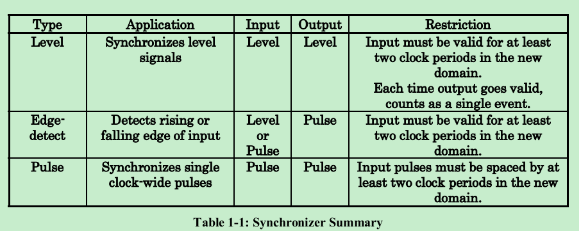

如果从逻辑设计角度简单来说就是加两级DFF。称为同步器吧。具体细分为level synchronizer/edge-detect synchronizer/pulse synchronizer 电平/边沿检测/脉冲。

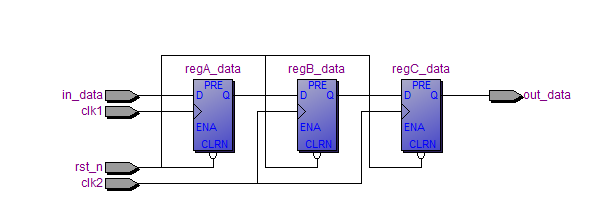

Level synchronizer:电平同步器

|

注意地方就是1,regA_data与regB_data之间不能有组合逻辑;2,regB_data与regC_data的时钟必须为同一个时钟的同一个采样延,即不能是一个上升沿另一个却用了下降沿;3,同步器中级联的寄存器中除了最后一个寄存器外的所有寄存器只能有一个扇出,即regA_data只能驱动regB_data,regB_data只能驱动regC_data一个;4,保险起见,第一级输入的电平信号应保持大于两个同步时钟周期。

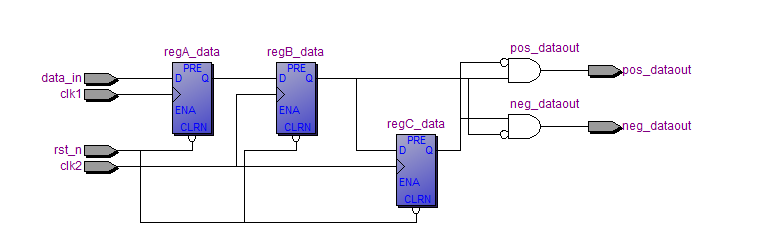

Edge-detect synchronizer:边沿同步器,

|

输入脉冲的宽度必须大于同步时钟周期与第一个同步触发器所需保持时间之和。最保险的脉冲宽度是同步器时钟周期的两倍。如果输入是一个单时钟宽度脉冲进入一个较慢的时钟域,则这种同步器没有作用。

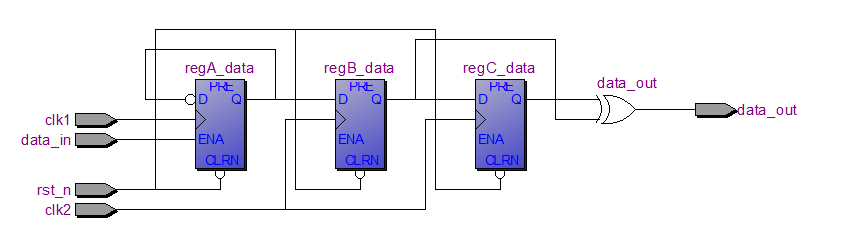

Pulse synchronizer:脉冲同步器

|

从某个时钟域取出一个单时钟宽度脉冲,然后在新的时钟域中建立另一个单时钟宽度的脉冲。输入脉冲之间的最小间隔至少为两个新时钟周期,否则会输出一个有两个同步时钟周期宽度的脉冲。