基于DSp的单相spll

0赞数字锁相的目标是使输出电流与电网电压同频同相,也即让逆变电流去跟踪电网电压的变化。输出电流频率是通过调整产生SPWM的三角载波频率而实现的,若电流频率小于电网频率,则应减小发生SPWM信号的相关定时器周期寄存器的值,从而通过提高三角载波频率来实现输出电流领率与电网电压频率相同,反之亦然。输出电流相位是通过调整产生SPWM信号正弦波离散值中的第一个点发生的时刻而实现的,当捕获到电网电压的过零点时,立即调整相应比较寄存器中正弦波离散值的指针,并作一定的时间补偿。

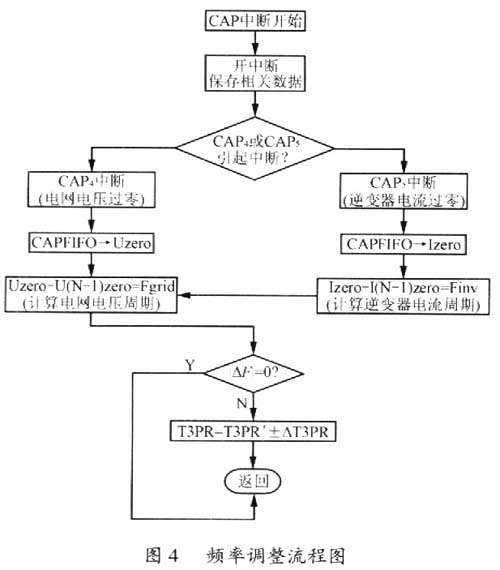

频率调整的软件流程框图如图4所示。

频率调整的过程是,当捕获到上升沿产生中断时,进入中断服务程序,先保护现场,再判断中断源是CAP4还是CAP5。若是CAP4,则说明产生中断的时刻是电网电压的过零点。将捕获值存入Uzero寄存器,再减去上一次的捕获值,两者的差值正好是电网电压的周期。然后拿该周期与当前逆变电流周期作比较,倘若两者无差值,则返回;若有误差,则对周期寄存器作相应的调整。

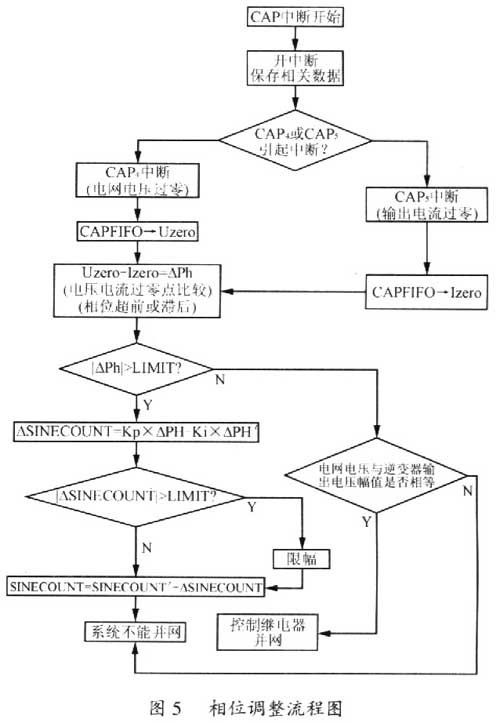

相位调整的软件流程框图如图5所示。相位调整的过程是,将当前电网电压与逆变电流两者捕获的过零值作比较,得到相位差。若相位差小于等于允许值,则说明两者已同相;若相位差大于允许值,则作PI调节,然后再判正弦计数值有无大于限制值,若无,则直接把相邻两次的差值作为调整量;若大于限制值,则只凋整限制值,在下一中断时,再作进一步的调整。

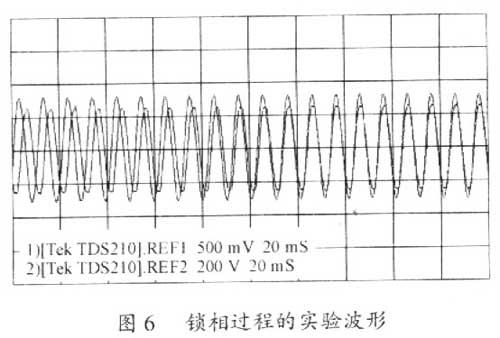

本文采用载波比N=400的SPWM同步调制技术,DSP芯片的CLOCK为40MHz(即周期25ns),三角载波最小计数单位为l,基波频率为50Hz(即周期20ms),因而正弦波的最小相位差为:400×2×25ns=20μs,(20μs/20ms)×360°=0.36°。即数字锁相精度为:O.36°/360°=0.1% 。锁相过程实验波形如图6所示。

本文采用载波比N=400的SPWM同步调制技术,DSP芯片的CLOCK为40MHz(即周期25ns),三角载波最小计数单位为l,基波频率为50Hz(即周期20ms),因而正弦波的最小相位差为:400×2×25ns=20μs,(20μs/20ms)×360°=0.36°。即数字锁相精度为:O.36°/360°=0.1% 。锁相过程实验波形如图6所示。