高级FPGA设计——第一章:高速度结构设计

2赞我们使用FPGA,除了实现预期功能之外,最关心的就是系统运行的速度,这是我们使用FPGA的最重要的原因。

FPGA中速度包含3个指标:

流量(Throughput):每个时钟周期处理的数据量,度量为每秒的位数。

时滞(Latency):数据输入到处理完的数据输出之间的时间,度量是时间或者时钟周期。

时序(Timing):时序元件(带有时钟端口的元件)之间的逻辑延时。我们首要关注关键路径(最大延时路径)的延时,这些延时包括组合逻辑延时,时钟到输出延时,布线延时,建立时间,时钟偏移等。时钟的度量是时钟周期和频率。

高流量设计:

高流量设计的主要方法就是流水线设计,下面我们通过一个例子来看流水线设计是如何提高流量的。

例:求X的三次幂

非流水线版本

性能:流量=8/3(位/时钟);时滞=3时钟;时序=关键路径中一个乘法器延时。

流水线版本

性能:流量=8/1(位/时钟);时滞=3时钟;时序=关键路径中一个乘法器延时。

这意味着,对于一个n次迭代算法,采用流水线结构可实现流量的n倍增加。同时不会导致时滞以及时序的恶化。唯一的代价就是增加面积。

低时滞设计:

所谓低时滞,就是最小化处理时间,让数据从输入端尽可能快速的传递到输出端。

还是以三次幂为例子,若采用组合逻辑:

性能:流量=8/1;时滞=在1和2个乘法器延时之间,0时钟;时序=关键路径中2个乘法器延时。

可以看到,低时滞设计也可以使流量保持在高水平,但会引起时序上的损失。

时序:

时序指的是一个设计的时钟速度,设计中任何两个时序元件间的最大延时将决定最大时钟速度。时钟速度过大将会导致系统不稳定,这也是我们常常困扰的问题,因此时序问题非常重要。

改善时序性能有如下方法:

(1) 添加中间寄存器到关键路径

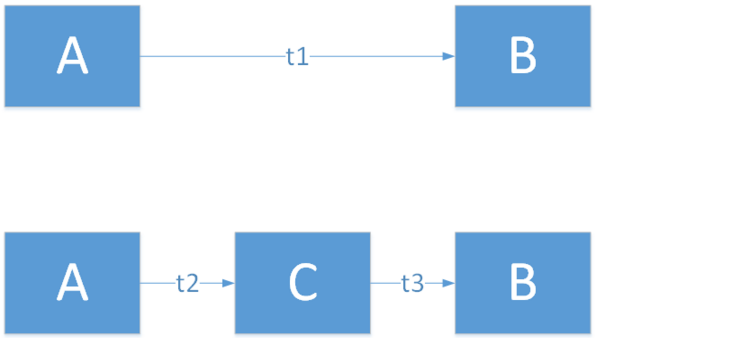

如图所示,AB为两个寄存器。第一种情况,AB之间延时为t1,则对该路径来说,最大时钟频率为1/t1(计算有简化)

第二种情况,在AB之间插入寄存器C,则对路径AB来说,最大时钟频率为1/t2,1/t3之间的最小值。t2+t3=t1,因此,最大时钟频率得以提升(计算有简化)。

(2) 并行结构

当时序不满足要求时,我们还可以重新组织关键路径,以致并行地实现逻辑结构。

如一个8位的二进制乘法器,设输入为X,X={A,B},A是高位字段,B是低位字段。

因此X*X={A,B}*{A,B}={(A*A),(2*A*B),(B*B)}

这样延时就从8位乘法器的延时缩短为4位乘法器的延时,进而提高了最大时钟频率。

(3)展平逻辑结构

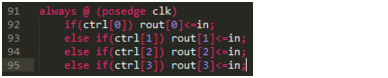

有一种逻辑称为特权逻辑,即有优先权的逻辑:

若ctrl的4位有且仅有1位会被置1,则可以展平逻辑结构

对于第一种情况,电路结构将包含一个大的选通器。而对于第二种情况,选通器将由4个小选通器组成。类似并行结构,可减小延时,提高最大时钟频率。

(4) 寄存器平衡

因为最大时钟频率取决于最坏条件路径,因此可以平衡各个寄存器间的逻辑来减少延时。简单来说,就是把最坏路径上的任务分点给其他路径来做。

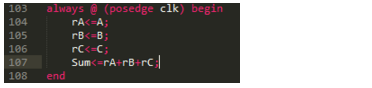

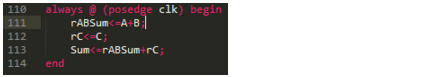

对于下面代码,第一个寄存器级是由rA,rB,rC组成,第二级由Sum组成。

明显,第二级的运算比较复杂,所以其延时也会较大。因此可以考虑把第二级的部分运算放到第一级来做,如下:

第二级路径延时降低,最大时钟频率因此提高。

(5) 重新安排路径

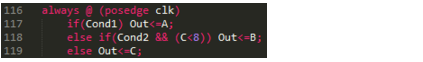

对于下面逻辑:

假设关键路径在C和Out之间,由一个比较器和两个门串联组成,最后连接到判决的mux.

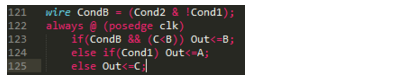

若修改逻辑如下:

则路径示意图如下:

关键路径上只有一个比较器和一个门,相较于之前逻辑,减少了一个门,从而可提高最大时钟频率。