高级FPGA设计——第三章:功耗结构设计

0赞除了速度和面积外,数字设计中还有另外一个主要特性:功耗。

在CMOS技术中,动态功耗与门和金属引线的寄生电容充放电有关。在电容中消耗电流的一般方程为:I=V*C*f (其中I是总电流,V是电压,C是电容,f是频率)

在FPGA设计中,电压一般是固定的,因此一般通过改变C和f来改变I,进而改变功耗。其中电容C直接与随时被触发的门的数量以及连接这些门的布线长度有关,频率f直接与时钟频率有关。具体降低功耗的方法如下:

1, 时钟控制

根据前面所提到的,被触发的门的数量以及时钟频率都会导致功耗的增加。那么显然,当某个模块在某一阶段无作用时,直接停止那个模块的时钟,将可以实现降低功耗的目标。

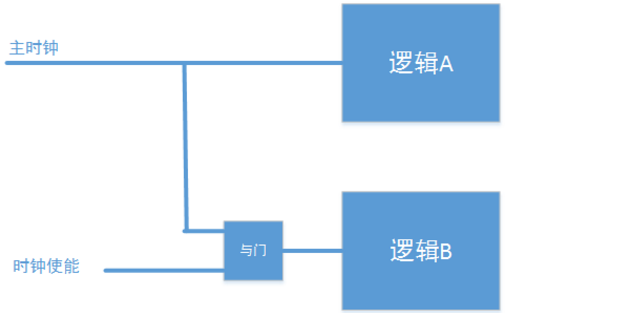

示例如下(不推荐该方法,只是为了说明原理),可以通过时钟使能信号来停止逻辑B部分的时钟,进而降低功耗。

但是时钟在FPGA中时神圣不可侵犯的,你不能随随便便给时钟加个与门来控制时钟的停止,推荐以下2种办法:

(1) 利用触发器的时钟使能引脚

(2) 利用全局时钟的多路选择器,即xilinx中的BUFGMUX元件

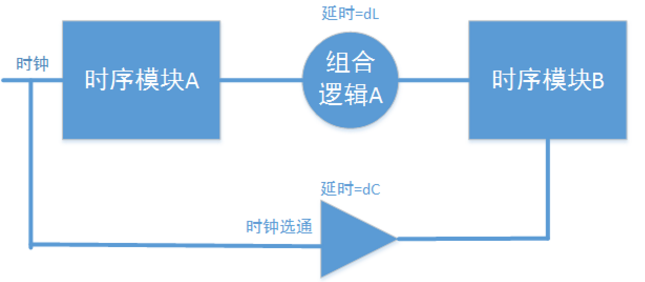

虽然选通时钟的方法很简单,但也会引入新的时钟域,并将产生时钟偏移的问题:

时钟偏移在时序逻辑中时十分重要的概念。

如下图所示,在不考虑其他因素的情况下,理论上时序模块A与时序模块B之间的时钟信号传播延时应为0。

假设初始状态下时序模块A的输入为a,时序模块B的输入为b,a在经过组合逻辑后变为c。

则理论上:第一个时钟沿,时序模块B采样的输入为b,在第二个时钟沿采样的输入为c。

但现在由于加了时钟选通模块,时钟延时将增加dC。若dC较大,大于dL。

则当第一个时钟沿发生时,时序模块A首先执行相应操作并通过组合逻辑把值c传递到时序模块B。因为dC>dL,等c传递到时序模块B后,模块B的第一个时钟沿才到达,因此时序模块B采在第一个时钟沿采样的输入为c,与理论不符,即引起电路的 失效。

2,输入控制

这个方法牵扯到CMOS的截止区/线性区/饱和区等理论,我不懂,所以直接说结论吧——必须为输入缓冲器接一确定值,不能使之悬空。

3,减少供电电压

动态功耗随着电压的减小平方减弱,因此在允许范围内,降低电压时最有效的降低功耗的办法。

4,双沿触发触发器

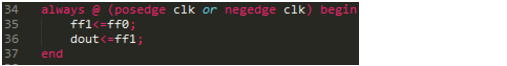

由于降低时钟频率可显著减低功耗,若采用双沿触发触发器,可将时钟频率降低一半,进而降低功耗。实现代码如下:

但需要注意的是不是所有器件都包含双沿触发器,若选定的器件不含双沿触发器,综合工具应该会报错。