VGA接口及其FPGA驱动

0赞最近调试vga输出模拟视频,学习经验整理如下。

开发环境:Quartus II 13.1 (64-Bit) + Nios II 13.1 Software Build Tools for Eclipse

1. VGA显像原理

显示器通过光栅扫描的方式,电子束在显示屏幕上有规律地从左到右、从上到下扫描。在扫描过程中,受行同步信号控制,逐点往右扫,完成一行扫描的时间倒数为行频;同时又在行同步脉冲期内回到屏幕的左端,从上往下形成一帧,在垂直方向上受场同步信号控制,完成一帧的时间倒数为场频。图像的显示过程即为在电子束扫描过程中,将地址与图像的像素依次对应,每一个被寻址的像素只获得其自身的控制信息,而与周围的像素不发生干扰,从而可以显示稳定的图像。

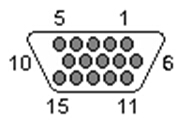

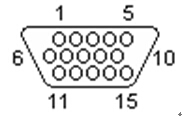

VGA接口是显示卡上输出模拟信号的接口,也叫D-Sub接口。这种接口上面共有15个针孔,分成3排,每排5个,通过模拟VGA接口显示图像的工作原理,将计算机内部以数字方式生成的显示图像信息,通过显卡中的ADC转变为R、G、B三基色信号和行、场同步信号, 通过电缆传输到显示设备中。

2. 显示器端口VGA管脚定义

针脚 | 名称 | 描述 | |

1 | RED | 红色分量信号 | |

2 | GREEN | 绿色分量信号 | |

3 | BLUE | 蓝色分量信号 | |

4 | N/C | 未使用 | |

5 | GND | 地线 | |

6 | GND R | 红色分量地线 | |

7 | GND G | 绿色分量地线 | |

8 | GND B | 蓝色分量地线 | |

9 | +5V | 电源(未使用) | |

10 | GND | 地线 | |

11 | N/C | 未使用 | |

12 | SDA | 串行数据信号 | |

13 | H SYNC | 水平同步(行同步) | |

14 | V SYNC | 垂直同步(场同步) | |

15 | SCL | 串行时钟信号 | |

母头(孔) |

公头(针) | ||

一般情况下,VGA线缆端都是公头,所以板端一般选用母头连接器。

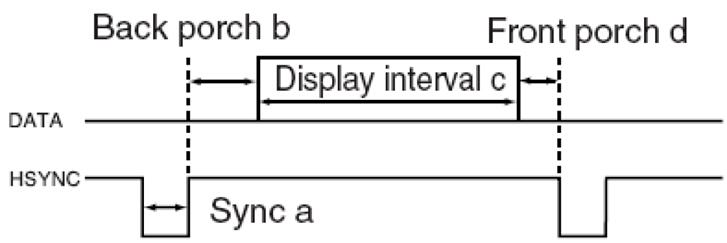

3. VGA时序

然而,要想驱动VGA,可不是那么容易的,需要满足VGA时序,一般情况下需要搭载存储器对数据进行缓存以满足VGA时序。

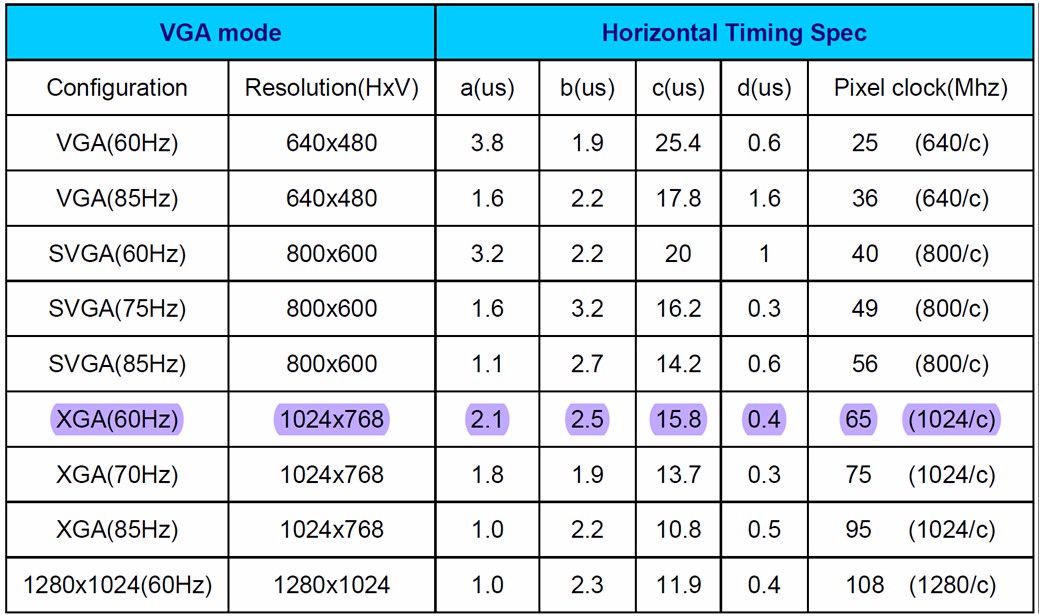

VGA的时序包括水平时序和垂直时序,且两者都包含的时序参数有:水平(垂直)同步脉冲、水平(垂直)同步脉冲结束到有效显示数据区开始之间的宽度(后沿BP)、有效显示区宽度、有效数据显示区结束到水平(垂直)同步脉冲宽度开始之间的宽度(前沿FP)。水平有效显示区宽度与垂直有效显示区宽度逻辑与的区域为可视区域,其他区域为消隐区。

不同分辨率、帧频对应不同的像素时钟,如分辨率为640×480,帧频为60Hz,则像素时钟为25MHz

4. VGA输出的FPGA实现

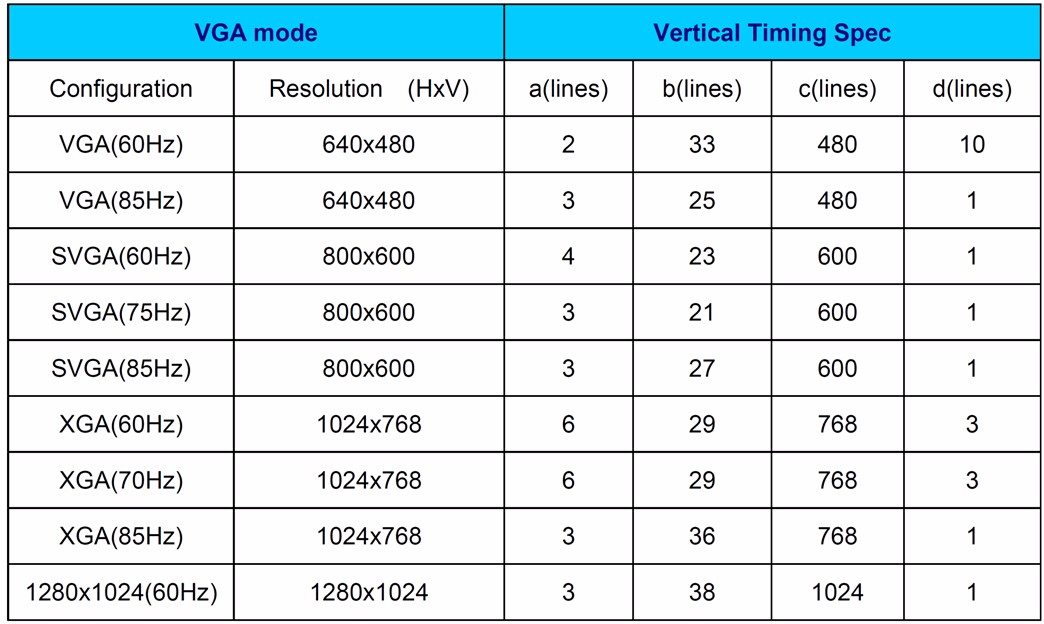

VGA输出图像方便,实用,因而很多设备都使用VGA来输出模拟视频信号,ADV7123为数模转换芯片,内置3路10bit DA,使用原理图如图所示。

FPGA通过VGA输出模拟视频需输出以下信号:

VGA_CLOCK

VGA_BLANK

VGA_SYNC

VGA_R[9:0]

VGA_G[9:0]

VGA_B[9:0]

VGA_HS

VGA_VS

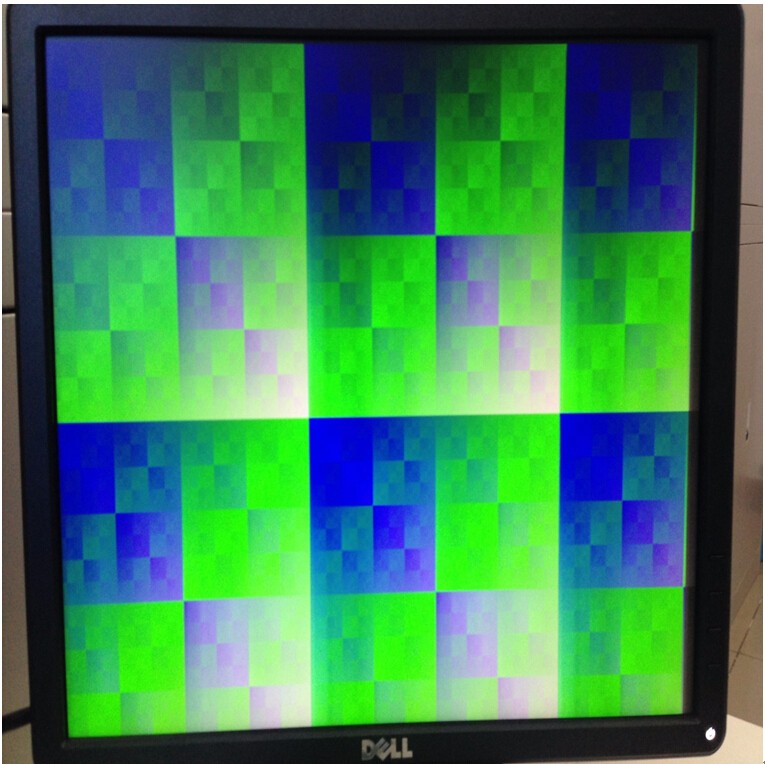

由于手头没有相应探测器,所以在FPGA内部模拟产生一幅图像,然后将其输出,VGA显示图像如下图所示。