基于FPGA的原理图PCB设计【连载4】——PCB设计

0赞原理图画完,就进入PCB了,allegro通过网表(netlist)的方式将原理图信息导入到PCB。关于FPGA的PCB设计几乎纯粹是体力活了,大致步骤如下

1. PCB库文件下载

2. 设置层叠结构

3. 设置约束,包括线宽、线距、走线的过孔的距离,过孔和焊盘的距离等

4. 器件摆放,包括器件对齐等操作

5. 走线,时钟线、电源线、差分线、等长线

(1) 封装文件下载

FPGA footprint可以从官网上下载,比如我用cadence画Altera家EP4CE115F29I7N,780pin,下载device_family_footprints.zip,里面就有对应780的fbga780.dra。

https://www.altera.com/support/support-resources/download/board-layout-test/pcb/pcb-cadence.html

(2) 设置层叠结构

电路板工程新建好之后,一般先设置层叠结构,带BGA封装FPGA的板子,一般至少布6层,如果有DDR的话,考虑要布等长,可能要布8层,10层,12层。6层的话,层叠结构一般为:

Top

Gnd1

Signal

Power

Gnd2

Bottom

(3) 设置约束

Physical constraint set|all layers下过孔栏添加过孔,我一般使用8mil-16mil过孔。

信号线宽一般为5mil(0.127mm)。

线距约束也一般为5mil。

如果有差分线的话,也需要有此处设置约束,差分约束设置步骤如下:

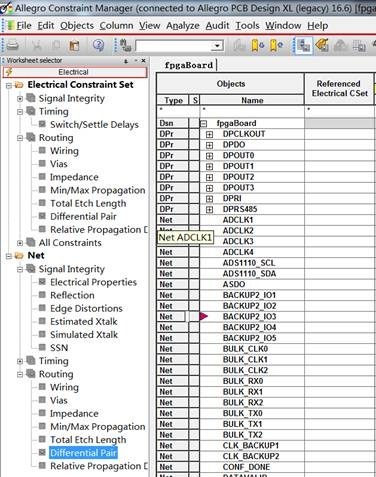

a) Net下选中differential pair

b) 执行菜单命令,objects|create|differential pair

c) 点击auto setup,前辍prefix输入DP,filter分别输入“+”和“-”,点击create,就自动创建了差分对。

d) 同样还是在Net下,选中routing,将差分对的uncoupled length和primary gap设置为0.254mm。

e) 添加完约束,走线时就会自动按差分线来走了,为差分线添加过孔的方式比较特殊,走线时单击右键,选择via pattern,一般选择水平和垂直两种。

(4) Placement

器件摆放很简单,一般在绘原理图前器件摆放位置就已规划好,原理图连接时尽量按照规划好的布局来连,这里主要说一说对齐摆放的技巧。

在布局时,为了美观,一般会进行器件对齐,执行菜单setup|application mode|placement edit,把要对齐的器件都选上,对着基准器件右键,选择align conponents即可。

Allegro功能非常强大,很多功能需要慢慢挖掘!!!

(5) connect

一般先走时钟线,再走信号线,线宽都为0.127mm。

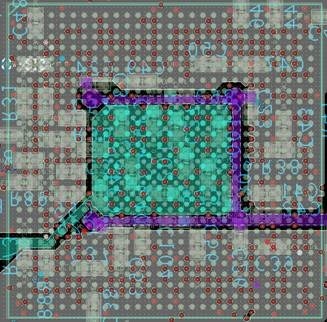

电源部分在内电层Vcc铺铜,3.3V,2.5V,1.2V铺铜如下图所示。