Wishbone总线地址译码

0赞连载目录篇:http://blog.chinaaet.com/justlxy/p/5100051808

在很多总线标准中,从设备必须译码所有的地址,这称为全地址译码。比如在PCI总线中,每一个从设备都必须具有32位的地址输入,并对这32位的地址进行译码以确定如何响应主设备的请求。

片上总线规范比如Wishbone规范支持部分地址译码。在部分地址译码总线规范中,从设备只需要译码自己所使用的地址空间。比如如果一个从设备只有4个地址,它就只需译码2比特地址而不是32位地址。这样做的好处是:地址译码速度快,地址译码逻辑少,从设备可自由定义地址总线宽度。

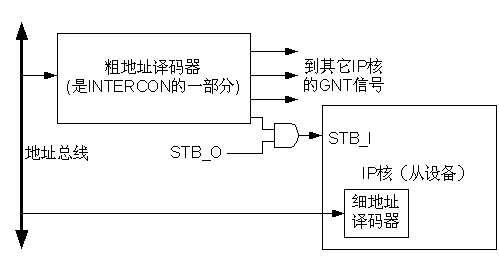

图26 Wishbone部分地址译码的实现

Wishbone部分地址译码的实现如图26所示。对于图中所示IP核,我们假设其只有4个地址,对应4组寄存器。地址译码器首先译码出其地址并给出选择信号,该选择信号与共享总线的STB_O相与输入到IP核的STB_I。而地址总线的最低2位被直接连接到IP核,IP核再根据这两位译码出当前操作选中的是具体哪个寄存器。

Wishbone共享总线示例中的仲裁器可以设计如下:

//the ACMP0 is for slave0: Flash

//the ACMP1 is for slave1: SRAM

module address_decoder2S(addr_i,ACMP0,ACMP1);

input [31:0]addr_i;

output ACMP0,ACMP1;

parameter ADDR_LOW_S0=32'b0;

parameter ADDR_HIGH_S0=32'h1FFFFF;//2M space for Slave 0;

//the rest of the space for Slave 1,so we do not need a dummuy slave;

assign ACMP0=addr_i<=ADDR_HIGH_S0;

assign ACMP1=~ACMP0;

endmodule