DDR扫盲——DDR中的名词解析

6赞RAS: Row Address Strobe,行地址选通脉冲;

CAS: Column Address Strobe,列地址选通脉冲;

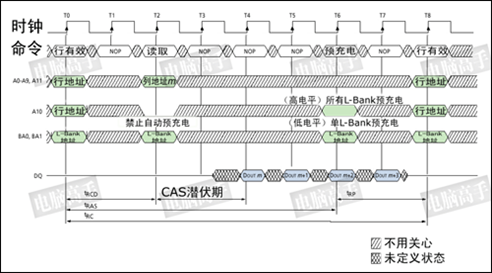

tRCD: RAS to CAS Delay,RAS至CAS延迟;

CL: CAS Latency,CAS潜伏期(又称读取潜伏期),从CAS与读取命令发出到第一笔数据输出的时间段;

RL: Read Latency,读取潜伏期;

tAC: Access Time from CLK,时钟触发后的访问时间,从数据I/O总线上有数据输出之前的一个时钟上升沿开始到数据传到I/O总线上止的这段时间;

tWR: Write Recovery Time,写回,保证数据的可靠写入而留出足够的写入/校正时间,被用来表明对同一个bank的最后有效操作到预充电命令之间的时间量;

BL: Burst Lengths,突发长度,突发是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(SDRAM),在DDR SDRAM中指连续传输的周期数;

Precharge:L-Bank关闭现有工作行,准备打开新行的操作;

tRP: Precharge command period,预充电有效周期,在发出预充电命令之后,要经过一段时间才能允许发送RAS行有效命令打开新的工作行;

AL: Additive Latency,附加潜伏期(DDR2);

WL: Write Latency,写入命令发出到第一笔数据输入的潜伏期;

tRAS: Active to Precharge Command,行有效至预充电命令间隔周期;

tDQSS: WRITE Command to the first corresponding rising edge of DQS,DQS相对于写入命令的延迟时间;

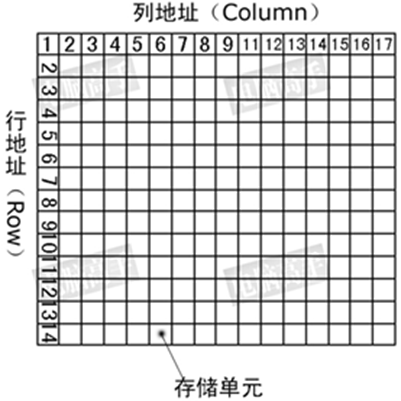

逻辑Bank

SDRAM的内部是一个存储阵列,要想准确地找到所需的存储单元就先指定一个(row),再指定一个列(Column),这就是内存芯片寻址的基本原理。

芯片位宽

SDRAM内存芯片一次传输率的数据量就是芯片位宽,那么这个存储单元的容量就是芯片的位宽(也是L-Bank的位宽);

存储单元数量=行数*列数(得到一个L-Bank的存储单元数量)*L-Bank的数量也可用M*W的方式表示芯片的容量,M是该芯片中存储单元的总数,单位是兆(英文简写M,精确值是1048576),W代表每个存储单元的容量,也就是SDRAM芯片的位宽,单位是bit;

DDR SDRAM内部存储单元容量是芯片位宽(芯片I/O口位宽)的一倍;

DDR2 SDRAM内部存储单元容量是芯片位宽的四倍;

DDR3 SDRAM内部存储单元容量是芯片位宽的八倍;

DDR4 SDRAM内部存储单元容量是芯片位宽的八倍。