DDR扫盲——DDR3基础知识

3赞

Burst Length可以设置为固定的BC4和BL8,也可以设置为“on the fly”,此时在发送读命令或者写命令时,可以通过A12/BC引脚进行切换BC4或者BL8。

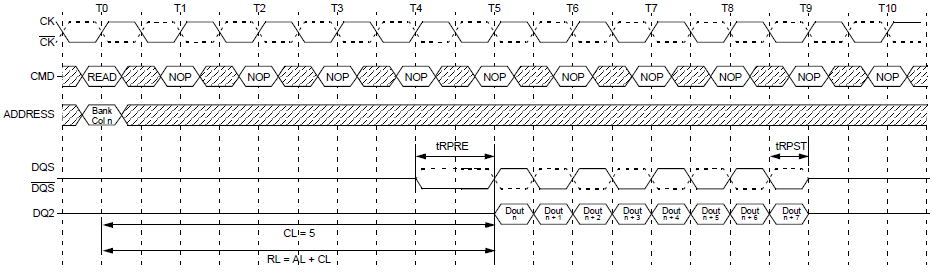

RL为总的读取潜伏期,其被定义为Additive Latency(AL)+CAS Latency(CL);

CAS Latency为读取潜伏,为内部读命令和第一个bit有效数据输出之间的时钟周期;

![]()

Additive Latency为附加潜伏期,它的作用为使命令和数据总线更有效,即允许读或者写命令紧跟有效命令;

CAS Write Latency(CWL)列写潜伏期,被定义为内部写命令和第一个bit有效数据输入之间的时钟周期延时;DDR3 SDRAM 不支持半周期潜伏,总的写潜伏为Write Latency(WL)=Additive Latency(AL)+CAS

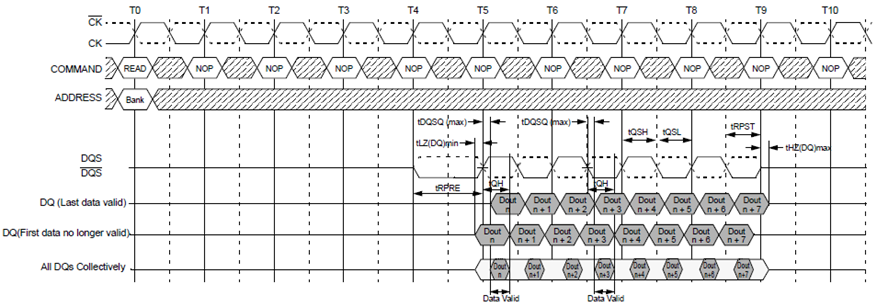

•tDQSCK是差分时钟的交叉点到数据选通脉冲的交叉点的时间;

•tQSH是DQS的差分输出高电平时间;

•tQSL是DQS的差分输出低电平时间;

•tDQSQ是最近数据选通脉冲到数据有效的时间;

•tQH是数据选通脉冲到最早的无效数据无法正确判断数据是否为1的时间;

读时序

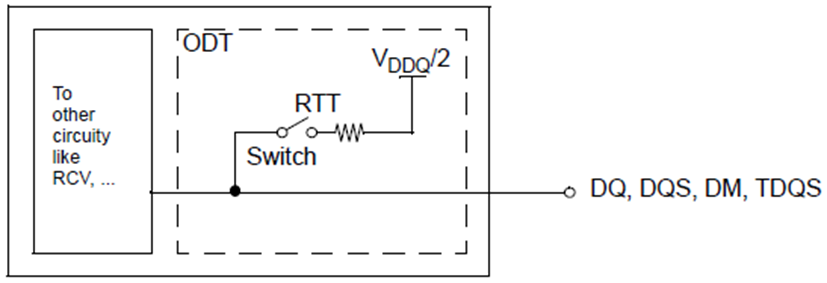

ODT(On-Termination)提供打开和关闭终结电阻的功能,该功能只为DQ、DQS、/DQS和DM管脚开放;

地址/命令建立时间、保持时间和降额

tis(total setup time)=tis(base)+ ∆tis

tih(total setup time)=tih(base)+ ∆tih

数据建立时间、保持时间和降额

tDS(total setup time)=tDS(base)+ ∆tDS

tDH(total hold time)=tDH(base)+ ∆tDH