静态时序分析的基本概念和目的

2赞静态时序相关博文连载目录篇:http://blog.chinaaet.com/justlxy/p/5100052092

很多初学者学习FPGA基本上都是沿用单片机或者ARM的C语言开发思想,编写好HDL程序,直接综合、MAP、PAR然后产生下载文件,直接下载到开发板上调试。有些人可能会进行一些功能仿真或者使用嵌入式逻辑分析仪来简单的分析一下时序。当设计规模较小,系统运行频率较低的时候,这样的开发过程可能不会带来什么问题,但是当设计规模稍微大一点,频率稍微高一点呢?可能就会出现各种意想不到的问题……

我记得在本科期间初学FPGA的时候,有很多初学者甚至这样说:FPGA只能做一些简单的东西,复杂的做不了,对此,我想说……他们却振振有词:你看,时序仿真出现这么多毛刺!!!

关于毛刺和亚稳态,可以看一下这篇博文:

http://blog.chinaaet.com/justlxy/p/5100052018

那么今天,我们就来聊一聊关于预防和解决毛刺与亚稳态等时序问题的方法——静态时序分析(Static Timing Analysis,STA)和时序约束。由于内容较多,所以决定以连载的形式发布……

如题,今天要聊的是一些最基础的东西,什么是静态时序分析?为什么要进行静态时序分析?静态时序分析有哪些基本概念?

废话不多说,进入正题:

1、静态时序分析是什么鬼?

首先,静态时序分析是一种验证方法,其基本前提是同步逻辑设计(异步逻辑设计需要制定时钟相对关系和最大路径延时等,这个后面会说)。静态时序分析仅关注时序间的相对关系,而不是评估逻辑功能(这是仿真和逻辑分析干的活!)。无需用向量(激励)去激活某个路径,分析工具会对所有的时序路径进行错误分析,能处理百万门级的设计,分析速度比时序仿真工具块几个数量级。在同步逻辑情况下,可以达到100%的时序路径覆盖(一般至少要求95%的时序约束路径覆盖,这个后面会详细说)。静态时序分析的基本目的是找出隐藏的时序问题,根据时序分析结果优化逻辑或约束条件,使得设计到达时序闭合(Timing Closure,也有人翻译为时序收敛)。静态时序工具可以识别的时序故障要比仿真多得多,包括:建立/保持和恢复/移除检查(包括反向建立/保持);最小和最大跳变;时钟脉冲宽度和时钟畸变;门级时钟的瞬时脉冲检测;总线竞争与总线悬浮错误;不受约束的逻辑通道等。有一些静态时序工具还能计算经过导通晶体管、传输门和双向锁存的延时,并能够自动对关键路径、约束性冲突、异步时钟域和某些瓶颈逻辑进行识别与分类。

2、有哪些静态时序分析工具?

Synopsys公司的PrimeTime和Mentor Graphics公司的SST Velocity主要用于全芯片的IC设计。PrimeTime是业界最为流行的分析工具。Innoveda公司的Blast工具主要用于FPGA和板级设计,它可支持单层和多层板结构,能链接板级交叉耦合分析。Altium公司的工具主要用于PCB设计中静态时序分析……各大FPGA厂商(Intel(前Altera)、Xilinx、Lattice、MircoSemi(前Actel))的IDE均提供静态时序功能,国内的京微雅阁等厂家目前好像还不支持,基本上用的都是第三方的静态时序分析工具。总的来说,FPGA的静态时序要比IC设计的静态时序简单的多,一般也不会分析到导通晶体管、传输门和双向锁存的延时这个层次上。

3、时序驱动FPGA设计流程

以Lattice的Diamond为例,简单地介绍一下静态时序分析在时序驱动的FPGA设计流程中所处的环节,具体的流程图如下:

如图所示,一般来说FPGA中的静态时序分析都有两个步骤,即Post-MAP和Post-PAR,分别对应的是图中的MAP TRACE和PAR TRACE。这张图里面的其他步骤的意义会在后面单独拿出来讲,包括SDC文件、LPF文件、PRF文件、甚至是TPF文件等的具体作用,综合过程中指定的时序约束(包括HDL中的和SDC中的)与MAP过程的时序约束有什么样的关系等内容。

暂时,我们需要知道的是,MAP TRACE和PAR TRACE的关系:从功能上来说,它俩干的事同样的事情,就连输出的分析报告内容基本都是相似的。但是MAP TRACE是在MAP之后,PAR之前的,所以其所需要的分析时间较少,分析精度较低;与之对应,PAR TRACE实在PAR之后,其所需要的分析时间较长(主要是PAR要花较多的时间),分析的精度较高。一般来说,在设计前期,我们应该尽量用MAP TRACE进行分析,此时发现的错误大部分都是产生于HDL设计过程中的。当MAP TRACE分析中基本上没有错误,其时序约束覆盖率大于95%(这个后面会详细说)时,可以再用PAR TRACE进行分析,该过程可能会发现一些在MAP TRACE过程中没有发现的时序问题。

4、静态时序分析的一些基本概念

首先放一张图,你能分析出图中每一个路径的时序关系吗?

很多初学者估计看了都会晕……不着急,后面我们会慢慢分析……首先介绍一下静态时序分析中的一些基本概念:(为了避免翻译带来的歧义,此处直接使用英文词汇了)

Launch vs. latch edges、Setup & hold times、Data & clock arrival time、Data required time、Setup & hold slack analysis、I/O analysis、Recovery & removal等。

具体介绍之前,再讲几个概念,首先来一张图:

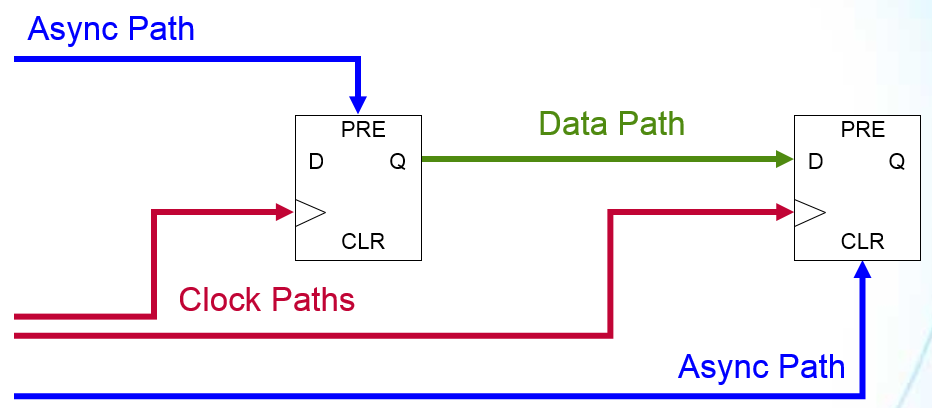

如图所示,一般有三种时序路径:时钟路径、数据路径和异步路径(一般指寄存器/触发器的异步控制信号,复位、重装载、清零等);两种分析模式:同步(Synchronous)和异步(Asynchronous)。

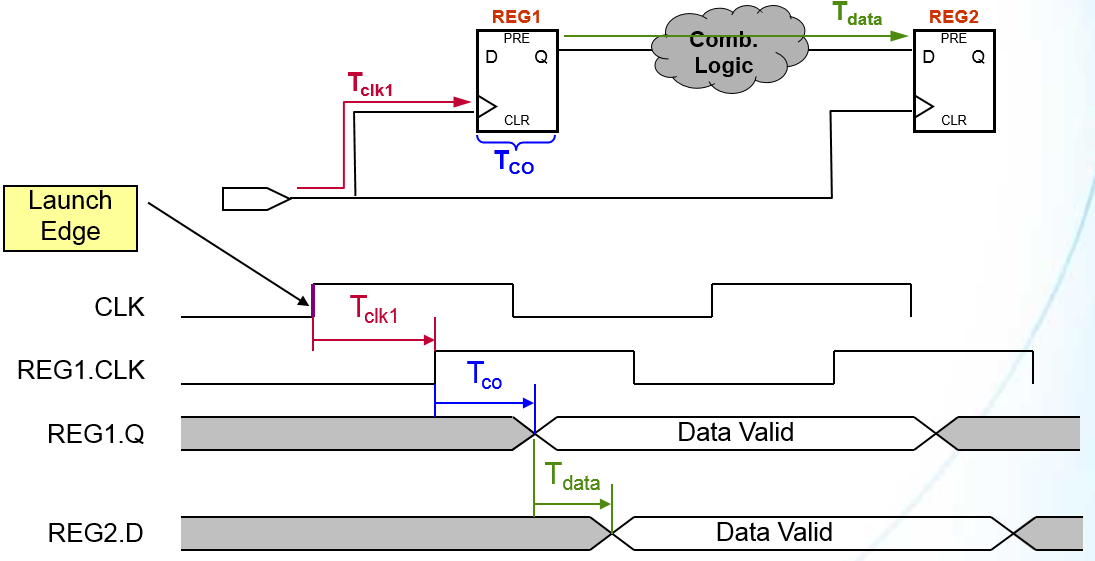

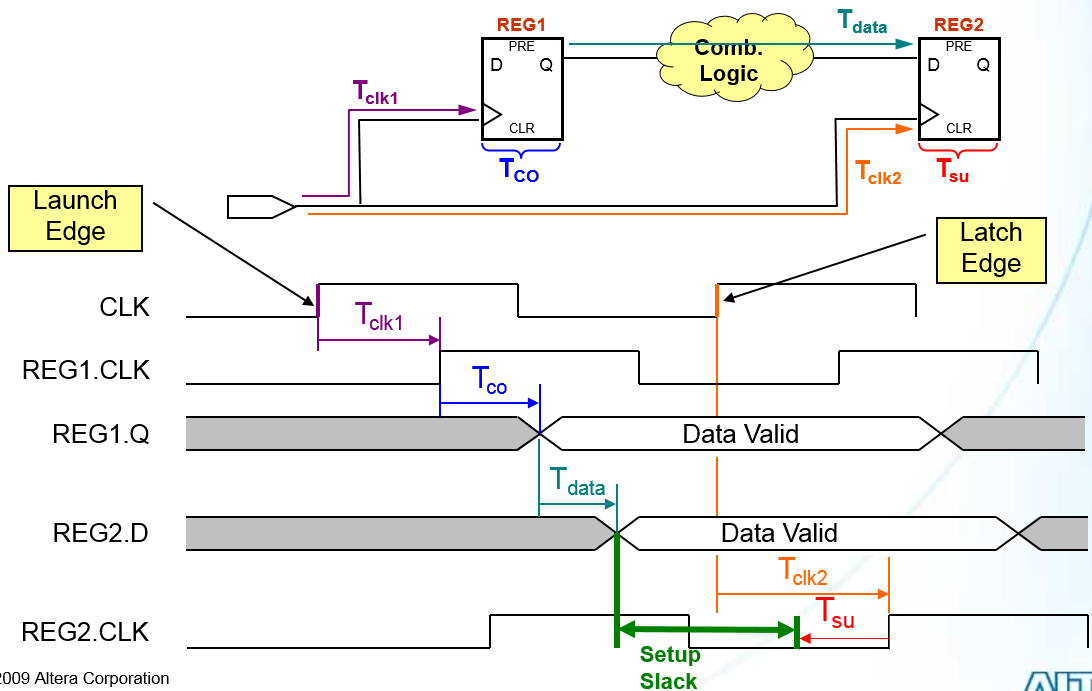

如上图所示,所谓发起边沿(Launch Edge)就是使数据从源寄存器(REG1)开始传输的时钟边沿;所谓锁存边沿(Latch Edge)就是目标寄存器(REG2)将数据锁存的时钟边沿。一般情况下,大部分的静态时序工具默认认为从Launch Edge到Latch Edge是一个时钟周期(即,数据需要在一个时钟周期内从REG1的Q,经过中间的组合路径,到达REG的数据输入端D,实际上还包括REG1的tco,这个后面讲),如果不能在一个时钟周期内到达呢?那么就属于多周期路径了,这就需要设计者提前告知分析工具,具体后面的连载博文会说。

如上图所示,建立时间(Setup Time)和保持时间(Hold Time)实际上是时钟边沿相对于数据的变化的时序关系。一般来说,建立时间和保持时间有两个角度去看,从器件(或者某个特定的模块)来看,一般认为建立时间是数据在时钟跳变沿到来前,最小的稳定时间;而保持时间则是数据在时钟跳变沿之后的最小保持稳定时间,分别记作tsu和th,如图所示。从时序分析的角度来看,建立时间和保持时间,就是实际的时间,及图中红色和蓝色框框所框出来的时间。静态时序分析的直接目的就是,分析实际的建立/保持时间是否满足器件(或者某个特定的模块)所需要的最小建立/保持时间。

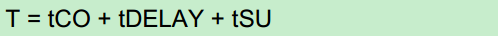

如上图所示,所谓数据到达时间(Data Arrival Time,Tdata)就是数据到达目标寄存器(REG2)的数据输入D端的时间,主要来源于其经过的组合路径的延时。一般而言,有如下的计算公式:

我们经常听别人说,这个电路最高可以运行多高的频率,那么,想知道这是怎么算出来的吗?且看下图:

上图是一个简化的同步逻辑延时模型,其中有

当时钟周期大于T,该模型可以正常工作,当时钟周期小于T,则不满足建立时间,该模型可能会经历亚稳态,甚完全不能正常工作。所以最高的时钟频率就是f=1/T。是不是很简单?

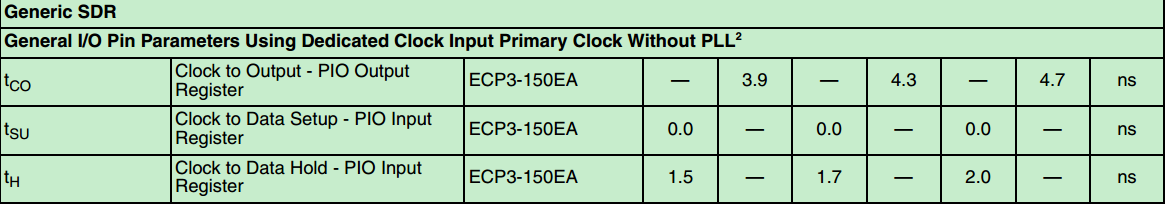

上面两张图中都出现的Tco叫做时钟到输出时间(Clock to Output Time),它和最小建立时间/最小保持时间一样,都和具体的器件特性相关。以Lattice ECP3为例,我们可以在LatticeECP3FamilyDataSheet的文档中找到如下信息:

当然,这只是Generic SDR部分的相关参数,其他的大家可以自行去查阅。

接下来,继续讲基本概念,接着看图:

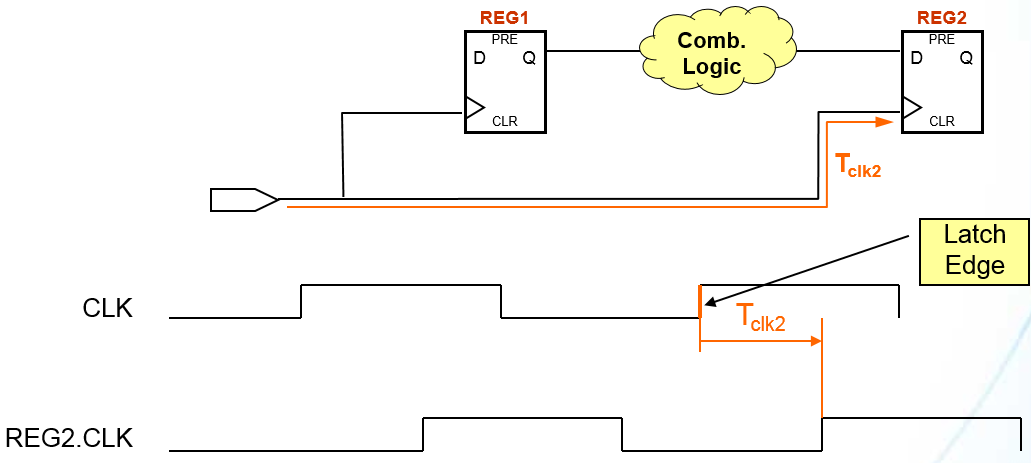

如上图所示:所谓时钟到达时间(Clock Arrival Time)是指,对应的时钟到达目标寄存器时钟输入端的时间,有如下的计算公式:

Tclk2主要是由于时钟走线较长,所带来的路径延时。在Lattice PFGA中,设计者可以通过使用时钟布线资源,而不是使用普通的布线资源来解决这个问题,具体的会在后面的博文中详细介绍。如果不可避免的带来了Tclk2,则必须通过添加CLK和REG2.CLK之间的关系的时序约束,告知时序分析工具。

所谓建立时间的松弛度(Setup Slack)就是指时间的建立时间和最小建立时间之间的关系。一般情况下,Slack为正值,则时序闭合(Timing Closure),当然也不是越大越好,具体后面会详细说;当Slack为负值时,则时序不闭合,即该电路不能正常工作或者存在亚稳态现象。

与Setup Slack相对应,还有Hold Slack,如上图所示。实际上,Setup Slack和Hold Slack是相互影响的,Setup Slack的值过大,很有可能导致Hold Slack的值过小,甚至是负值,进而导致时序不闭合!

前面讲的都是内部的逻辑关系,相对于板级延时,内部的路径延时还是比较小的。如上图所示,在实际的电路设计过程中,往往还要分析FPGA的IO的相关时序,这就需要设计者将Tclk1和Tclk2之间的关系和Tdata的数值通过时序约束的方式告知分析工具。

吃了个午饭回来,接着写,哈哈哈!

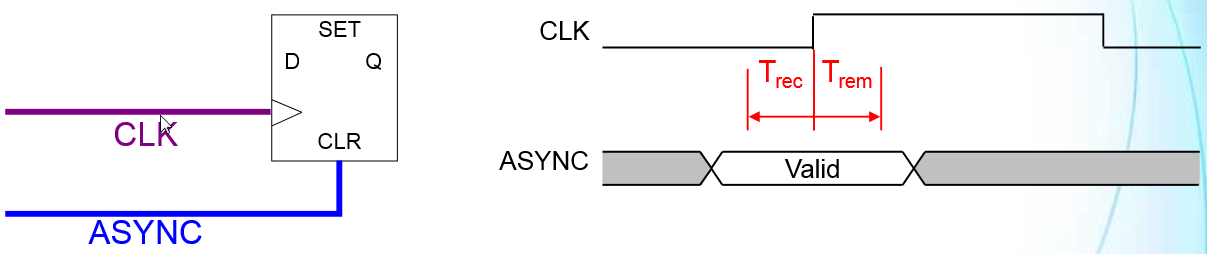

接下来讲恢复和移除(Recovery & Removal)时间,如上图所示。

恢复时间(Recovery Time)是指异步控制信号(如寄存器的异步清除和置位控制信号)在“下个时钟沿”来临之前变无效的最小时间长度。这个时间的意义是,如果保证不了这个最小恢复时间,也就是说这个异步控制信号的解除与“下个时钟沿”离得太近(但在这个时钟沿之前),没有给寄存器留有足够时间来恢复至正常状态,那么就不能保证“下个时钟沿”能正常作用,也就是说这个“时钟沿”可能会失效。

去除时间(Removal)是指异步控制信号(如寄存器的异步清除和置位控制信号)在“有效时钟沿”之后变无效的最小时间长度。这个时间的意义是,如果保证不了这个去除时间,也就是说这个异步控制信号的解除与“有效时钟沿”离得太近(但在这个时钟沿之后),那么就不能保证有效地屏蔽这个“时钟沿”,也就是说这个“时钟沿”可能会起作用。

换句话来说,如果你想让某个时钟沿起作用,那么你就应该在“恢复时间”之前是异步控制信号变无效,如果你想让某个时钟沿不起作用,那么你就应该在“去除时间”过后使控制信号变无效。如果你的控制信号在这两种情况之间,那么就没法确定时钟沿是否起作用或不起作用了,也就是说可能会造成寄存器处于不确定的状态(亚稳态)。而这些情况是应该避免的。所以恢复时间和去除时间是应该遵守的。

这实际上和建立时间与保持时间是对应的,对于大部分的器件(或某个特定模块)来说,可以近似的认为,最小建立时间与最小恢复时间相等,最小去除时间与最小保持时间相等。

5、补充说明

前面一直在说时序约束,那么时序约束到底是什么鬼呢?现在来简单介绍一下:

时序约束(Timing Constraints),是指在逻辑综合(Synthesis)、MAP、布局布线(PAR)或者静态时序分析时,在综合工具、HDL源码中、MAP或PAR工具以及静态时序分析工具(STA Tools)中指定信号的频率(或周期)、占空比、延时、异步时钟相位差、建立/保持时间、多周期以及最大路径延时等约束条件,EDA工具会根据设定的约束条件来进行工作。

·在综合工具(或者是HDL源码中的)中指定的时序约束条件,目标是使综合生成的电路满足时序约束要求;

·在MAP以及PAR工具中指定的约束条件,目标是使布局布线的结果满足时序约束要求;

·在静态时序分析工具(如Lattice的TRACE及Timing Analysis View)中指定的约束条件,目标是根据约束条件来分析设计是否满足要求。

时序闭合(Timing Closure)又称为时序收敛,是指通过在逻辑综合工具、布局布线工具中指定时序约束条件以进行综合和布局布线,然后根据静态时序分析的结果,经过优化设计或修改约束条件后,是设计满足时序约束条件。简单的所,时序闭合就是指设计满足时序约束条件。目前IC设计工具不断发展的方向也是,将逻辑综合、布局布线、静态时序分析精密结合在一起,使设计一次性达到时序闭合为最高目标。

关键路径(Critical Path)通常是指同步逻辑电路中,组合逻辑延时最大的路径。也就是说关键路径是对设计性能起决定性影响的时序路径。静态时序分析能够找出逻辑电路的关键路径,通过查看静态时序分析报告,可以确定关键路径。对于关键路径进行时序优化,可以直接提高设计性能(直观的提高就是电路的最高工作频率的提高)。对于同步逻辑常用的时序优化方法包括流水线(Pipeline,即向组合逻辑中插入寄存器,是一种以面积换取速度的常用手段,具体后面的连载博文会进行详细介绍)和Retiming两种方法(后面会详细介绍)。

原本还有一些内容的,但是这一篇写的实在是有点长了,所以放在后面的博文在写了。