填坑:你可能学了假的数字集成电路——从ISSCC文章分析数字电路与数字系统的区别(二)

1赞这个坑挖得太久了,但是一直没有时间填坑。期间很多朋友来催,但是都是只催不打赏。说明其实不是真心想问。真心想问的话我的知乎账号已经公布了,完全可以在知乎上向我付费提问嘛。虽然黑心的苹果要刮掉30%的地皮。从这一点可以看出“知识有价”“尊重知识”这些观念,还远远没有渗透到中国普通人的观念里面去。

昨天为了给新参加项目的研究生简单的做一个报告,凑合做了个简化版的PPT。于是也有了一点思路,正好今天出卷子出累了。就过来把这个坑稍微的给填一填。

ISSCC(International Solid-State Circuits Conference ,国际固态电路会议)是集成电路领域世界上最专业最顶级的会议,有“集成电路界的奥林匹克”之称。当然,什么叫固态电路呢?那么一定有气态电路咯!这个问题以后再谈。每年全球从事集成电路领域的顶级科研机构和各大公司,都会积极向这个会议投稿。很多顶尖的集成电路产品甚至是以“首发”的形式在这个会议上第一次亮相。

这个会议既然代表了集成电路领域的最高水平,那么这会上的一些信息就非常值得参考。研究这个会的一些现象,可以帮我们厘清很多东西。近年来由于中国大陆地区集成电路水平的持续提高和国家对于半导体、集成电路产业日益重视,研究这个会的各种自媒体、微信公众号也越来越多了。那么在这里呢,我只是从我的角度,从数字集成电路与数字系统的学习和研究的角度来分析一下这个会。

作为一个会议,最重要的就是委员会(committee)。Committee会负责这个会议的组织、审稿以及现场的一些主持和规划。而ISSCC由于涉及到了集成电路设计的各个领域,因此设置了各种各样的sub-committee.这些sub-committee分别是:Analog(模拟电路)、Data Converters(数据转换器)、Digital Architectures and Systems(数字架构与系统)、Digital Circuits(数字电路)、Imagers, MEMS, Medical & Displays(图像、微机电、医疗与显示)、Memory(存储器)、Power Management(电源管理)、RF(射频)、Technology Directions(技术发展)、Wireless(无线)、Wireline(有线)这几个。

其它的我们先不谈,我们可以看到,带有Digital这个单词的sub-committee其实是有两个。他们分别是:Digital Architectures and Systems和Digital Circuits。这两个sub-committee有什么区别呢?让我们一起来看看他们组织的分会到底有哪些。

Digital Architectures and Systems长期以来组织的分会主要是两个,一个就是长期万年不变的Processors,另外一个就是随着时代而不断演变的其它。2018年,这个其它的名字叫:Machine Learning and Signal

Processing;在2017年,其它的名字叫:Deep-Learning Processors ;在2016年,其它的名字叫:Next-Generation Processing;在2015年,由于Digital这边是按High Performance(高性能)和Energy Efficient(高能效)来划分的,就不好比较了。

在Processor这个Session里面,万年不变的是各大处理器公司过来秀他们的最新型号的处理器,Intel、AMD、IBM这些都是这个Session的常客。Feescale这些目前已经消失了的公司也多次在这个Session上面展示他们最新的处理器。处理器作为用途最广,设计最为精妙也最为复杂的一类数字集成电路,独占一个Session自然是无可厚非的。

而这个“其它” Session 主要是展示的什么呢? 主要是展示的除了处理器之外的“系统级”的数字集成电路。我们来看一下2018年最新录取的文章:

13.1 A Shift Towards Edge Machine-Learning Processing(转向边缘机器学习处理)

13.2 QUEST: A 7.49TOPS Multi-Purpose Log-Quantized DNN Inference Engine Stacked on 96MB 3D SRAM Using Inductive-Coupling Technology in 40nm CMOS(QUEST:一个7.49TOPS多用途对数量化DNN推理引擎,采用电感耦合技术在96nm三维SRAM上堆叠在40nm CMOS)

13.3 UNPU: A 50.6TOPS/W Unified Deep Neural Network Accelerator with 1bto-16b Fully-Variable Weight Bit-Precision(UNPU:具有1bto-16b全变量位精度的50.6TOPS / W统一深度神经网络加速器)

13.4 A 9.02mW CNN-Stereo-Based Real-Time 3D Hand-Gesture Recognition Processor for Smart Mobile Devices (用于智能移动设备的9.02mW基于CNN立体声的实时3D手势识别处理器)

13.5 An Always-On 3.8μJ/86% CIFAR-10 Mixed-Signal Binary CNN Processor with All Memory on Chip in 28nm CMOS(2.8μJ/ 86%CIFAR-10混合信号二进制CNN处理器 with 28nm CMOS芯片内存)

13.6 A 1.8Gb/s 70.6pJ/b 128×16 Link-Adaptive Near-Optimal Massive MIMO Detector in 28nm UTBB-FDSOI(基于28nm UTBB-FDSOI的1.8Gb / s 70.6pJ / b 128×16链路自适应近优化大规模MIMO检测器)

13.7 A 232-to-1996KS/s Robust Compressive-Sensing Reconstruction Engine for Real-Time Physiological Signals Monitoring(用于实时生理信号监测的232至1996KS / s鲁棒压缩感测重建引擎)

可以看到,7篇文章5篇和当下最新的机器学习相关,而剩下两篇,一篇是和5G相关的信号检测处理,另一篇则是生物信号处理。但从题目都可以看出,这些是偏向于应用的、比较完整的系统级设计。

而Digital Circuits这个sub-committee下面的组织了哪些Session呢?2018年主要是这么几个:Neuromorphic, Clocking and Security Circuits(神经形态,时钟和安全电路)、Adaptive Circuits and Digital Regulators等。

我们来看看Neuromorphic, Clocking and Security Circuits这个Session主要发了些什么:

7.1 A 0.0056mm2 All-Digital MDLL Using Edge Re-Extraction, Dual-Ring VCOs and a 0.3mW Block-Sharing Frequency Tracking Loop Achieving 292fs rms Jitter and -249dB FOM(采用边缘重新提取的0.0056mm2全数字MDLL,双环形VCO和0.3mW的模块共享频率跟踪环路实现292fs rms抖动和-249dB FOM)

7.2 A 0.02mm2 Fully Synthesizable Period-Jitter Sensor Using Stochastic TDC Without Reference Clock and Calibration in 10nm CMOS Technology(采用10nm CMOS工艺的无参考时钟和校准的随机TDC 0.02mm2完全合成周期抖动传感器)

7.3 A 0.3-to-1.2V Frequency-Scalable Fractional-N ADPLL with a Speculative Dual-Referenced Interpolating TDC(具有推测双参考内插TDC的0.3至1.2V频率可升级分数N ADPLL)

7.4 A 55nm Time-Domain Mixed-Signal Neuromorphic Accelerator with Stochastic Synapses and Embedded Reinforcement Learning for Autonomous Micro-Robots(具有随机突触的55nm时域混合信号神经形态加速器及自主微机器人嵌入式强化学习)

7.5An Enhanced-Security Buck DC-DC Converter with True-RandomNumber-Based Pseudo Hysteresis Controller for Internet-of-Everything (IoE) Devices(一种基于真随机数的伪随机控制器(IoE)的增强型安全降压DC-DC转换器)

7.6 A Secure Camouflaged Logic Family Using Post-Manufacturing Programming with a 3.6GHz Adder Prototype in 65nm CMOS at 1V Nominal VDD(一个安全的伪装逻辑系列使用后期制造编程3.6GHz加法器原型在1V标称VDD的65纳米CMOS)

7.7 A PUF Scheme Using Competing Oxide Rupture with Bit Error Rate Approaching Zero(一种误比特率接近零的竞争性氧化物破裂的PUF方案)

7.8 A 445F2 Leakage-Based Physically Unclonable Function with Lossless Stabilization Through Remapping for IoT Security(445F2基于泄漏的物理不可克隆功能,通过重新映射实现无损稳定,实现物联网安全)

这8篇文章从题目来看,前三篇和Digital PLL有关。实际上是在研究如何用数字器件(门电路)来实现时钟生成器。后四篇和安全有关,研究如何用数字器件(门电路或存储器之类的)来实现一些伪随机数、物理不可克隆等功能。第四篇从题目看是一个混合信号电路,但是现在看不到内容不好评价。

对比一下两个Session,就可以发现在Digital Circuits其实更关注底层的、电气特性上的内容。换言之,Digital Circuits更接近于设计电路,而Digital Architecture and System则有非常浓厚的系统和应用的背景。

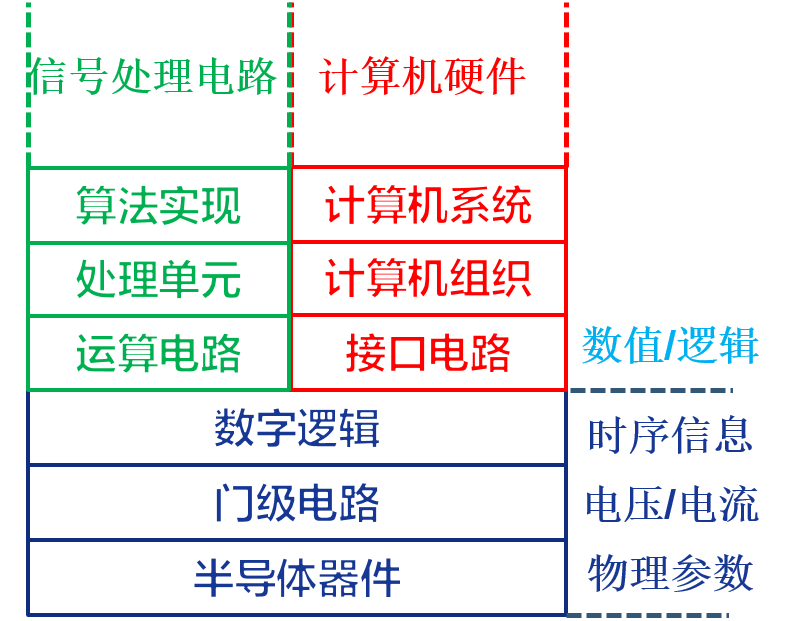

所以,这个时候我就需要上一张图了:

这是我简单的对数字集成电路与数字系统做的一个抽象图,不是很成熟,希望大家多提意见。

对比这张图,我们可以看到。以数字逻辑分界,可以简单的把数字电路与数字系统划分成两个层面。侧重于关心电路本身的物理参数、电压/电流以及时序信息的下面这部分,其实是属于数字电路的范畴。而已经将其抽象为0、1以后的布尔逻辑表示了,就更关心数值变化、逻辑功能这些的其实应该被叫做数字系统。

理论上来说,Digital Circuits这个sub committee应该是去关注下面三层的内容而Digital Architecture and System应该是关注上层的。但由于ISSCC这个会议强调电路实现、强调实测参数的特殊性,没有一些物理参数、电气指标是上不了这个会的。所以实际上能在ISSCC上发表到Digital Architecture and System组织的这两个Session的文章其实得从门级做到算法实现/计算机系统这个层面。而且几乎在每一层都要有所创新。所以真正能在ISSCC上发表一篇系统级集成电路设计的文章,别的不说,能协调组织起能在这么多层次上创新和工作的人才就非常难得。当然,其实有一些并不关注底层电气特性而更强调从结构、组织、系统上创新的会议,真正做数字系统的人是大量的在这类会议上发表高水平文章。比如计算机体系结构的几大顶会,EDA和电子设计自动化的几个顶会之类的。这个以后有机会再讲。

最后需要强调的一点是,现在很多同学,尤其是微电子、集成电路专业的同学对数字设计的认识就只停留在数字逻辑这一个层次上。以为写写HDL代码,跑跑流程就叫做数字设计。往下,没有能力做电路;往上,没有能力做系统。实际上就把自己给困死在这里了。

今天先说到这里,下次找几个典型文章来做进一步的分析,从而更加明确因为所以做的工作不同而对人的知识背景、思维方式以及研究思路所提出的区别。并且会分析我国目前专业设置条件下,数字集成电路与系统方面人才培养的困境。