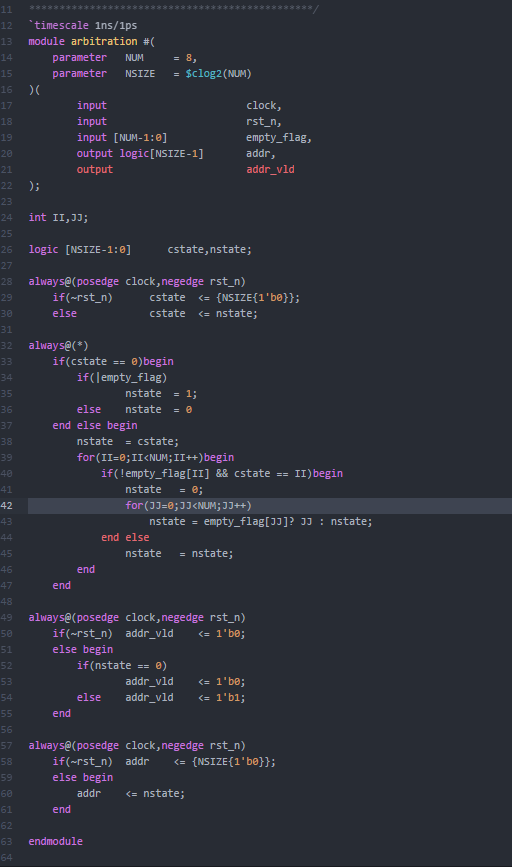

Verilog仲裁器,”极简主义“,看看我需要多少行代码

3赞

发表于 1/18/2017 4:48:48 PM

阅读(10483)

用途:仲裁器,优先级仲裁,非轮询仲裁,用于多路选择仲裁,DDR,AXI,AVALON这些,addr地址自动跳跃到下一个empty的通道。

1、可综合

2、自定义路数,数量无边界

3、几乎没人敢这么写......