聊一聊FPGA中除法器的设计(VerilogHDL篇)

1赞其实除法器并不是什么新鲜玩意了,网上关于除法器的博文也多了去了,也有好几种设计方法。有的挺实用,有的应用范围很有限,很难应用于大规模的程序设计中。今天要介绍的也表示什么高级算法,网上之前也有很多人讨论过了,不过基本上都是抄来抄去,有的里面甚至还存在错误,有的只是跑了遍功能仿真,提供的程序也存在较多的错误或者不合理的地方。其实,我也没干什么事,只是把前人的结果总结整理了一遍,把相关的程序规范了一下,无偿分享给大家,如果其中存在一些错误或者不合理的地方,欢迎大家和我交流!

设计的原理很简单,前人以经说的很明白了,这里就直接搬过来了:

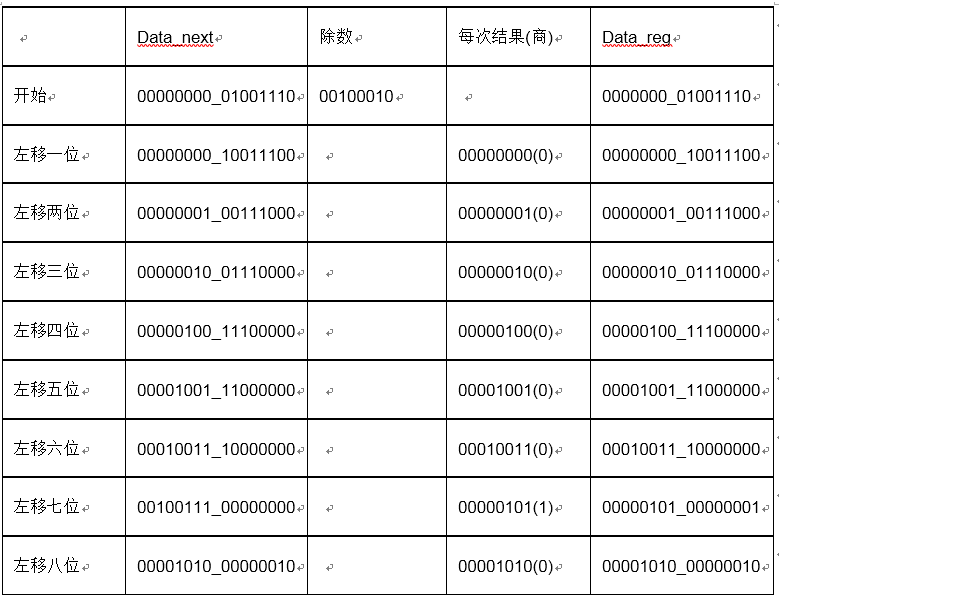

假设被除数与除数都是八位数据,这里的算法是:

将被除数,扩展成16位的数据,低8位为被除数的值,高八位的值全为0。有开始信号,对16位数据data赋值,然后开始运算。比较data的高八位和除数的值,如果大于0,说明被除数大,将此时商置1,赋值给data的最低位,然后将被除数高八位减去除数。然后将data向左移位一位,继续比较。最终计算8次后。Data的高8位数据就为所求的余数,低八位就为所求的商。

原理说白了就是:先移位,在比较(作差),迭代八次……

重要说明:本算法只支持正数,整数除法,需提前指定被除数和除数位数,且除数和被除数位数需相等。(改进的算法会在后期和大家分享)

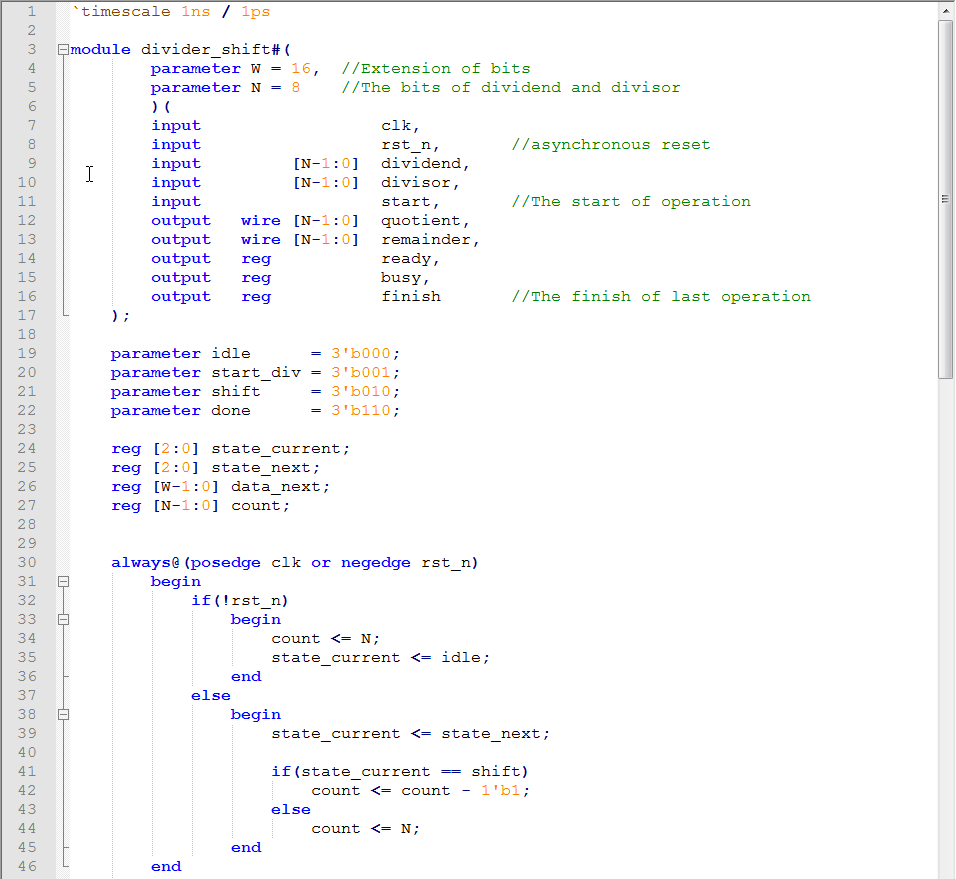

ChinaAET的代码语言功能太low,而且还不支持VerilogHDL,所以代码就直接贴图了:

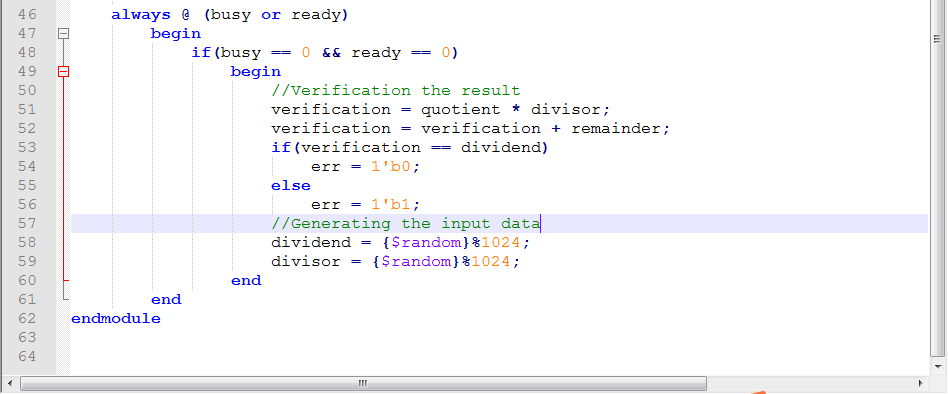

下面是Testbench:

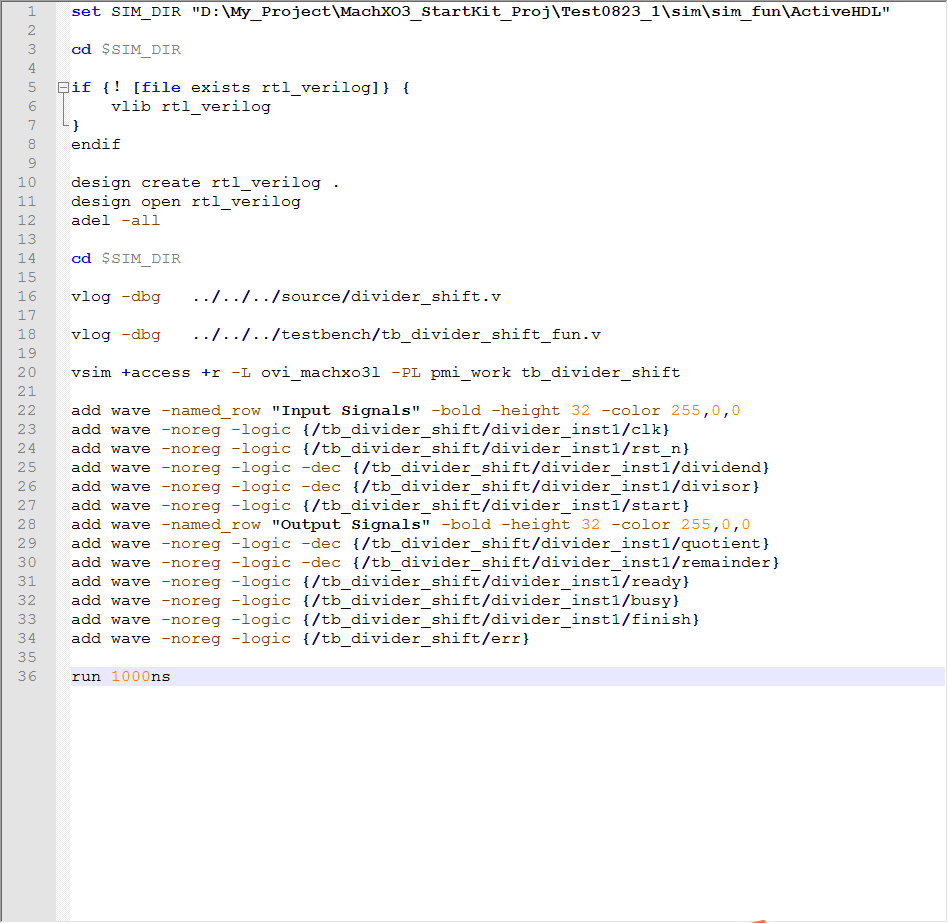

以及ActiveHDL的脚本文件:

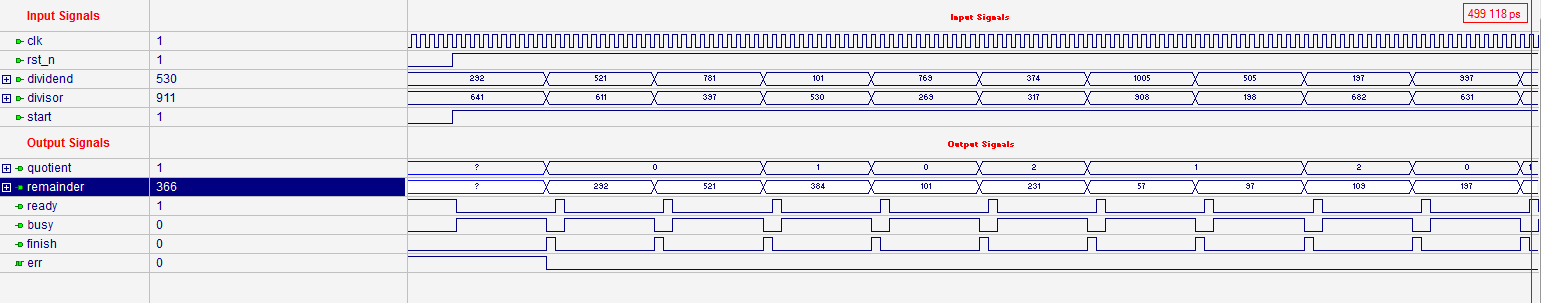

仿真结果如下:

使用Synplify Pro综合并Map之后得到(Diamond中,MachXO3 6900C):

Design Summary

Number of registers: 42 out of 7485 (1%)

PFU registers: 42 out of 6864 (1%)

PIO registers: 0 out of 621 (0%)

Number of SLICEs: 32 out of 3432 (1%)

SLICEs as Logic/ROM: 32 out of 3432 (1%)

SLICEs as RAM: 0 out of 2574 (0%)

SLICEs as Carry: 15 out of 3432 (0%)

Number of LUT4s: 63 out of 6864 (1%)

Number used as logic LUTs: 33

Number used as distributed RAM: 0

Number used as ripple logic: 30

Number used as shift registers: 0

Number of PIO sites used: 38 + 4(JTAG) out of 207 (20%)

Number of block RAMs: 0 out of 26 (0%)

Number of GSRs: 1 out of 1 (100%)