Lattice Diamond Reveal SerDes Debug Core简明教程(For ECP5)

3赞Lattice ECP5/ECP5-5G SerDes系列文章,目录篇:http://blog.chinaaet.com/justlxy/p/5100064954

本文将以Lattice ECP5为例,简要地介绍一下如何使用Diamond中的Reveal工具来调试SerDes/PCS。文中使用的Project在文章最后的附件中,Project是基于Lattice ECP5 Versa板写的,可以直接使用。

1、插入Reveal SerDes Core

使用Reveal SerDes Debug Core有一个基本前提:在使用Clarity配置SerDes/PCS的时候,必须使能SCI(SerDes Client Interface)端口。用户在完成RTL设计,确保设计可以没有错误(可以通过PAR)后,便可以在Reveal Inserter中插入Reveal SerDes Debug Core。如下图所示,在点击Add New Core之后,有两个选项,Add SerDes Debug便能插入Reveal Debug Core。需要注意的是,在插入Reveal SerDes Debug Core之前,需要先插入一个普通的Logic Analyzer Core。

点击Add Serdes Debug之后,可以看到:

之后两个信号需要输入,其中Sample Clock建议使用与Serdes/PCS无关的时钟,这里使用ECP5片内的OSC产生的时钟源。需要注意的是,SerDes Reset是高电平复位。

注:在SerDes Debug界面时,不要使用Signal Search功能,会导致Diamond闪退(部分版本)。

2、使用Reveal SerDes Core

插入成功之后,重新PAR,并生成bitstream,下载到板卡中,然后使用Reveal Analyzer工具,如下图所示:

红色圈出来的,便是与SerDes Debug Core相关的界面,其中SerDes Debug选项卡界面如下。左边的三个灯分别表示Tx PLL、Rx信号摆幅和CDR的状态,绿色表示正常,红色表示异常。

注:该界面显示的延时一般较大,对于部分比较窄的脉冲可能不会被显示出来。所以要确保相关信号有没有问题,最好的办法还是将相关信号作为Reveal的触发条件,进行调试。

用户可以通过此界面,修改SerDes/PCS的绝大部分参数,观察PLL/CDR的状态,还可以针对特定的模块进行复位。另一个选项卡Wishbone Debug的界面如下:

用户可以通过此界面实现对SerDes/PCS的寄存器的读写操作。

注:Tx Output to Rx 的Loopback模式有的时候会存在问题,原因是SerDes/PCS使用了Rx Loss of Signal作为Reset Sequence的输入,而Loopback设置为此模式时,Rx Loss of Signal将会持续为高电平,导致Reset Sequence逻辑无法正常工作,进而导致SerDes/PCS复位异常。

注:Diamond 3.10以及之前的版本中的Reveal,在部分Win10系统中会有较多的Bug,请使用Win7系统或者更新至Diamond 3.11。

3、关于TN1261 Table18中的错误

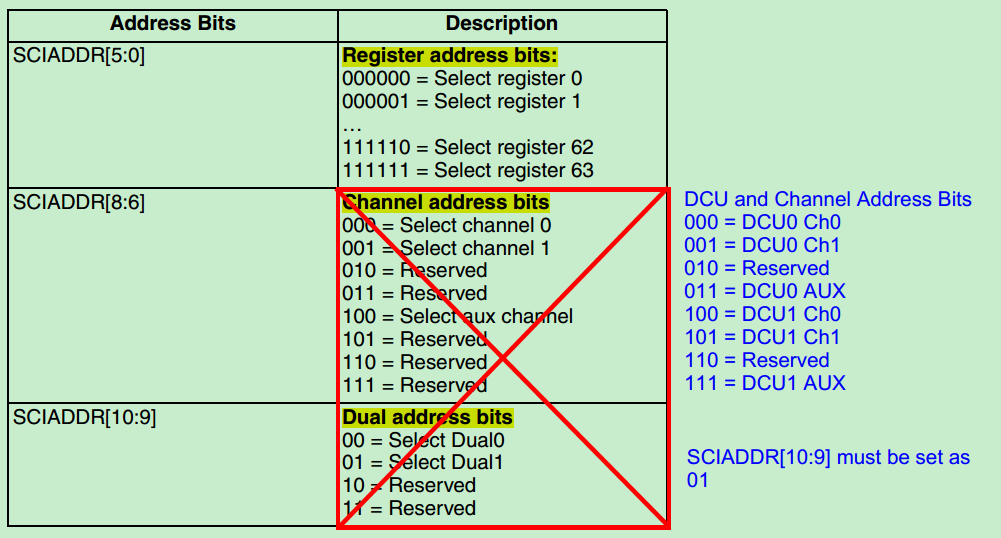

Lattice ECP5 and ECP5-5G SerDes/PCS UG(TN1261)中的Table18(SCI Address Map for up to four SerDes/PCS Duals)似乎存在一些错误,建议按照下图中蓝色字体的方式设置SCI地址:

4、关于ECP5/ECP5-5G SerDes/PCS的调试建议

使用Diamond 3.10以及Diamond 3.11配置ECP5/ECP5-5G的SerDes/PCS后,自动生成的Reset Sequence逻辑(在*_softlogic.v中)和Diamond 3.9/3.8存在较大差异。Diamond 3.10/3.11产生的Reset Sequence逻辑主要针对了部分5G的应用(PCIe Gen2等)做了优化,但是对于non-5G应用却起到了负面作用,可能会导致部分配置下的复位异常,CDR无法正常锁定等现象。所以,对于non-5G的应用,建议使用Diamond3.9配置生成SerDes/PCS。

4.1、用户首先要保证PLL Loss of Lock为稳定的低电平(可以用Reveal工具,设置该信号为上升沿触发),PLL Loss of Lock为高电平则表明Tx PLL失锁。而导致Tx PLL失锁最主要的原因便是参考时钟的问题,如时钟抖动过大,信号摆幅超出范围等时钟信号质量问题。参考时钟的问题也会进一步导致CDR无法正常工作,进而导致CDR失锁。

4.2、如上图所示,导致CDR失锁的另一个重要的原因是输入信号质量,如信号的摆幅超出范围,信号抖动过大等等。其中当信号摆幅超出范围时,Rx Loss of Signal也会变高,表明当前输入信号摆幅不符合要求。用户可以在SerDes/PCS配置界面或者Reveal SerDes Debug Core中调整Tx De-Emphasis、Tx阻抗,Rx阻抗,AC/DC耦合,均衡等设置,来改善输入信号的质量(如果输入信号到达ECP5之前已经很差,这种改善可能意义不大)。用户还可以重新设置Loss of Signal Detector的阈值,来观察该信号的变化。

4.3、需要注意的是,Reset Sequence逻辑主要以Rx Loss of Signal、CDR Loss of Lock、Tx PLL Loss of Lock和用户输入复位信号作为输入,进而产生复位输出信号给到SerDes/PCS的各个具体的模块。当上述三个信号出现异常,都可能会导致Reset Sequence逻辑重新复位,甚至复位异常。关于Reset Sequence的具体作用,用户可以参考ECP5 SerDes/PCS UG的相关章节。

4.4、用户如果发现,SerDes信号的P/N设计反了,可以在配置界面或者Reveal SerDes Debug Core界面使能PN翻转功能。

4.5、rx_disp_err_ch和rx_cv_err_ch信号表明发生了严重的错误,而导致错误的原因是输入信号质量不符合要求,用户可以调整3.2中所述的相关参数,看看是否能够改善。

4.6、在确保前述所有信号均正常,用户可以通过PRBS Check来评估各个通道的误码率(可以参考本文附件中的Project设计)。

4.7、注意SerDes/PCS的Rx和Tx分属两个不同的时钟域,在使用Reveal的时候请注意跨时钟域问题。包含SerDes/PCS的设计一般都是高速设计,请确保插入Reveal之后的整个设计,仍然能够通过时序分析。

本文所用的Project:(密码为LatticeSemiconductor)![]() ECP5_PCS_Test1.7z

ECP5_PCS_Test1.7z

注:需要更新ispClock的文件为:![]() ispClock_Versa_Demos_156p25MHz.7z

ispClock_Versa_Demos_156p25MHz.7z