关于桶形移位寄存器的讨论

0赞

发表于 7/28/2017 9:54:36 AM

阅读(5528)

桶形移位寄存器即循环移位寄存器,在浮点加减运算、压缩/解压缩和图像处理算法中有应用,所以稍微说明下:

例如设计一个8位桶形移位器:8位桶形移位器是有8个数据输入位,8个数据输出位和3个控制输入位的组合逻辑电路,其输出字等于输入字的循环移位,循环移位的次数由控制输入位指定。比如,如果输入字等于ABCDEFGH(每个字母表示一位),且输入控制位为101(5),则输出字为FGHABCDE。

学校里的一些教材给出的写法是:

module barrel_shifter(data,num,out);

input [7:0] data;

input [2:0] num;

output [7:0] out;

reg [7:0] out;

always @(data or num)

begin

case(num)

3'b000:out=data;

3'b001:out={data[6:0],data[7]};

3'b010:out={data[5:0],data[7:6]};

3'b011:out={data[4:0],data[7:5]};

3'b100:out={data[3:0],data[7:4]};

3'b101:out={data[2:0],data[7:3]};

3'b110:out={data[1:0],data[7:2]};

3'b111:out={data[0],data[7:1]};

endcase

end

endmodule然而,这样的设计并不能产生寄存器,综合出的结果只是纯组合电路。(不过可以通过综合指令或约束,保留寄存器)在Diamond下(使用LSE综合工具)得到的结果为:

从面积的角度来说,这种设计方式的确可以节省资源,但是在高速时序电路中。这样的设计就不是很合理了。

随着FPGA技术的发展,各个厂商已经为开发者提供了大量的IP、基本设计的功能块(原语)等。在包含DSP Slice的器件中,设计者可以很方便的使用DSP进行桶形移位寄存器设计。但是也有一些早期的FPGA或者是CPLD中并不包含DSP Slice的,但是厂商也为设计者提供了基本的功能块,在综合设计的时候,会自动识别用户设计,并用功能块进行例化。

下面给出另一种设计:

module BarrelShiftReg(clk,rst,din,rotate_cnt,reg_out);

parameter WIDTH = 8;

parameter CNT_SIZE = 3;

input clk,rst;

input [CNT_SIZE - 1:0] rotate_cnt;

input [WIDTH - 1:0] din;

output [WIDTH - 1:0] reg_out;

reg [WIDTH - 1:0] reg_out;

wire [WIDTH - 1:0] barrel,temp;

assign {barrel,temp} = {din,din} << rotate_cnt;

always @ (posedge clk or posedge rst)

begin

if(rst)

reg_out <= 0;

else

reg_out <= barrel;

end

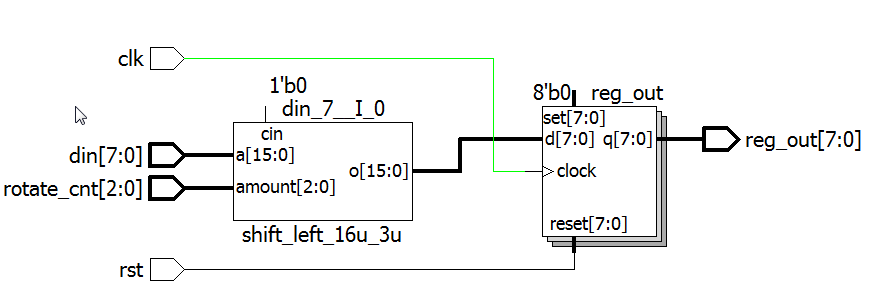

endmodule其综合结果如下图所示:

可以发现,综合工具将移位部门的设计自动替换为厂商提供的功能块。