静态时序分析中典型路径与时序优化技术介绍

1赞静态时序相关博文连载目录篇:http://blog.chinaaet.com/justlxy/p/5100052092

其实前一段时间,我写过一篇关于静态时序分析中的典型路径总结的文章(当时偷懒,直接截了几张图,哈哈哈):http://blog.chinaaet.com/justlxy/p/5100051960

今天写的这篇,作为连载博文的一部分,为了方便大家对后面的文章的理解,所以决定在之前文章的基础上做一些解释和说明。

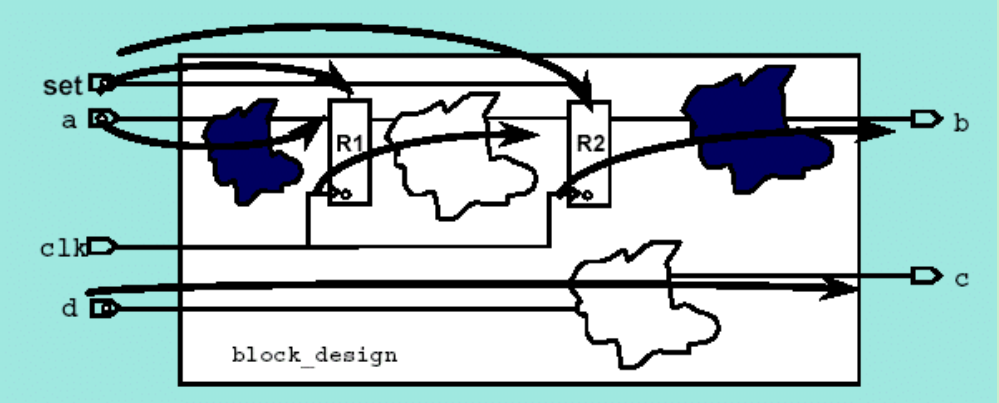

还记得在上一篇博文中的那张图不?

实际上和之前博文(关于静态时序分析中的典型路径总结的文章)中出现的这张是一样一样的:

其中,主要包含四种类型的时序路径:

输入端口到触发器(Flip-flop)、触发器到触发器、触发器到输出端口、输入端口到输出端口。

具体一点,主要有一下几种路径:

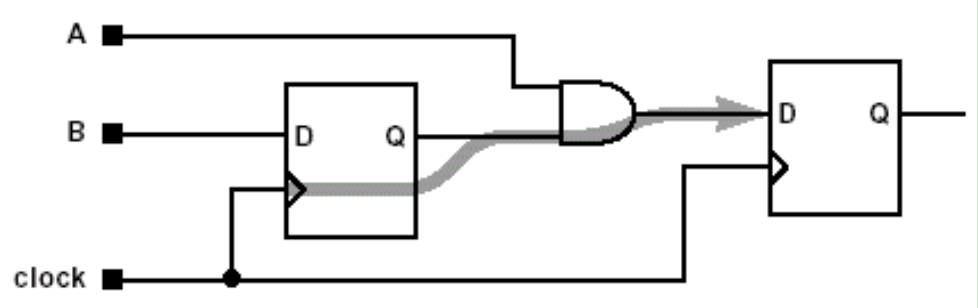

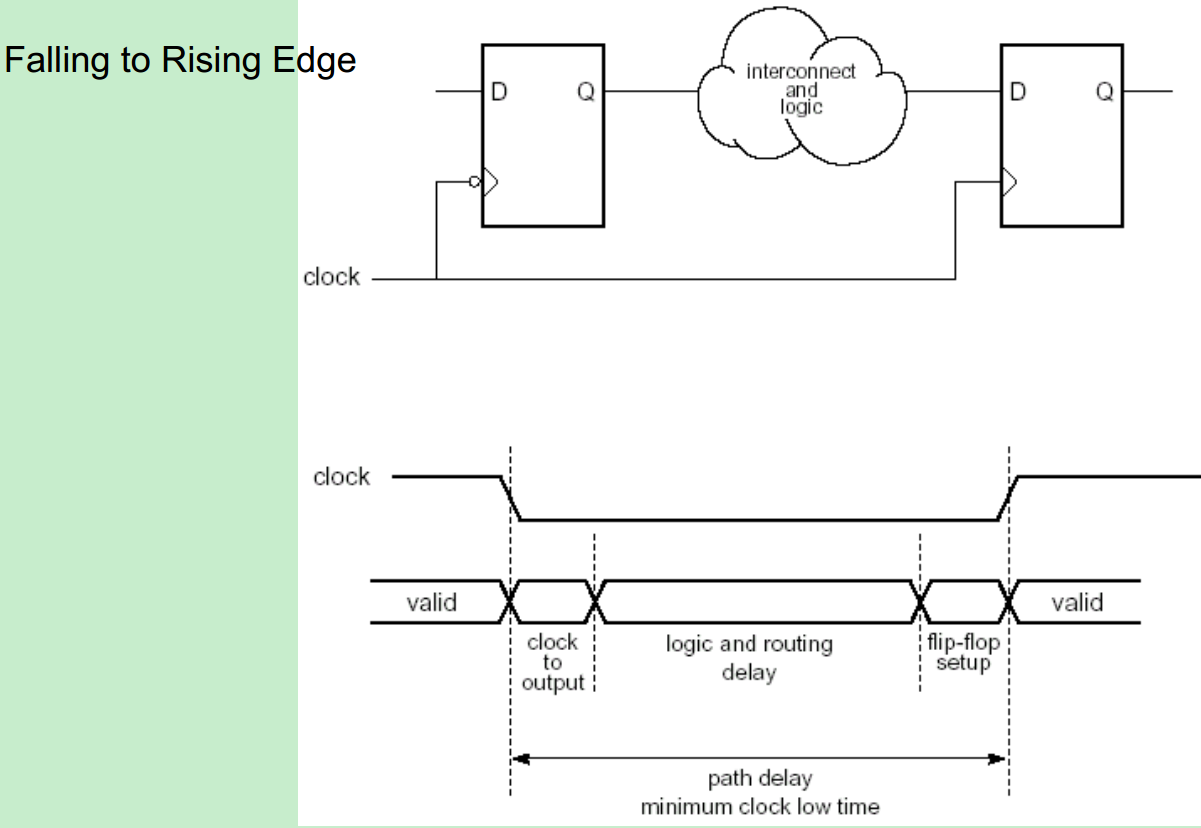

1、时钟到建立(Clock-to-Setup Path)

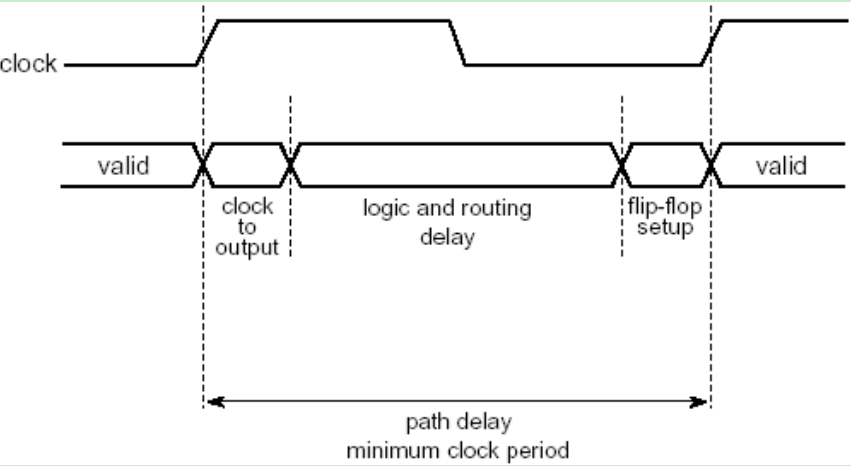

即图中灰色的路径。在大部分的电路设计中,一般都单独使用时钟的上升沿或者下降沿作为触发信号。此时有:

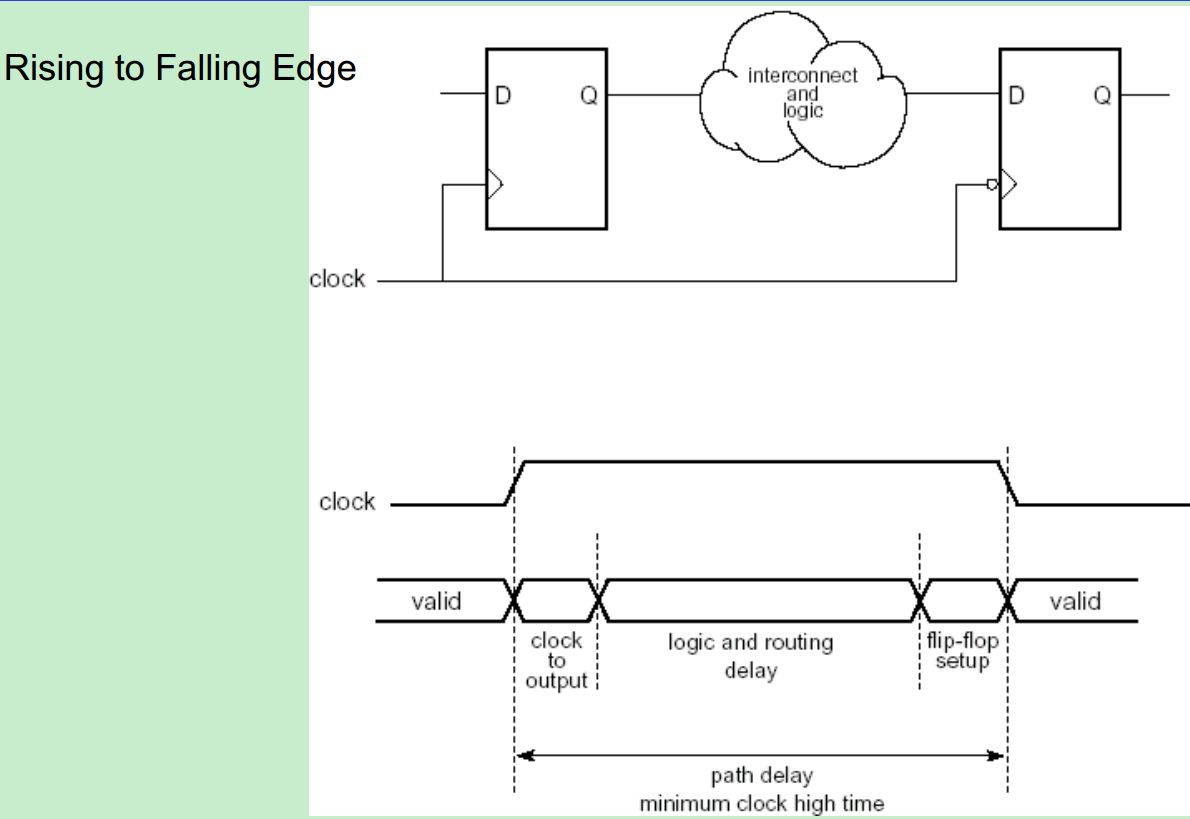

但是也有一些场合同时使用时钟的上升沿和下降沿作为触发信号的(如DDR),此时:

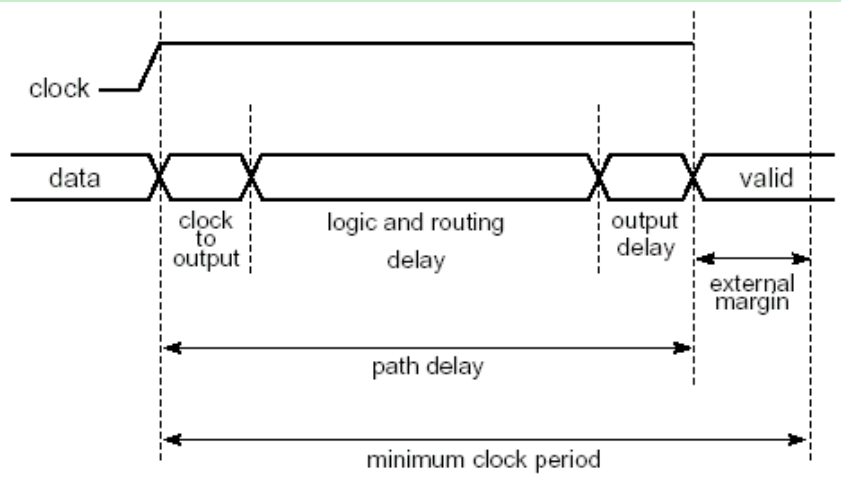

2、时钟到管脚(Clock-to-Pad Path)

时序图为:

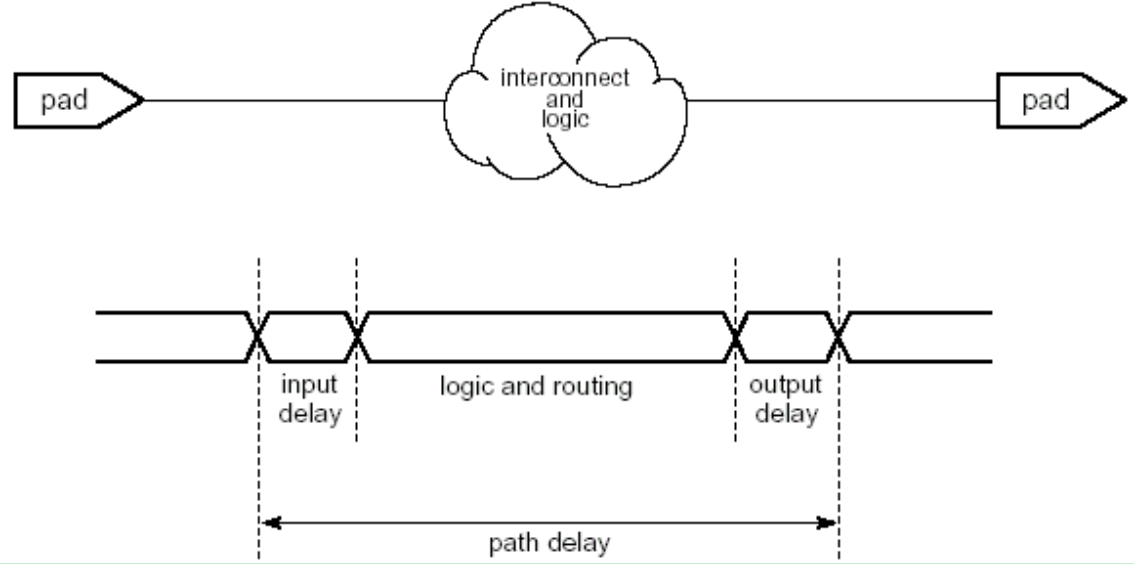

3、管脚到管脚(Pad-to-Pad)

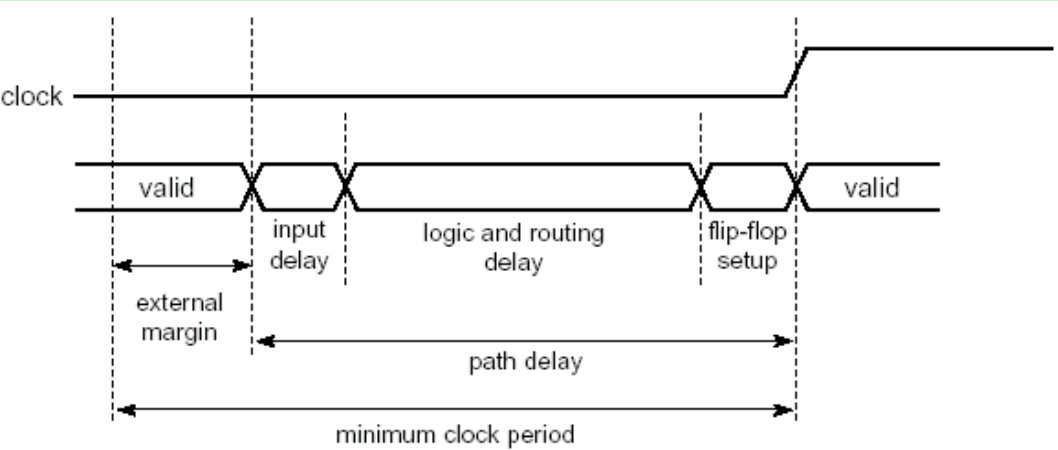

4、管脚到建立(Pad-to-Setup)

5、存在时钟偏移(Clock Skew)或者异步时钟输入的情况

在上一篇博文中有提到了两种时序优化方法,这里来简单地介绍一下:

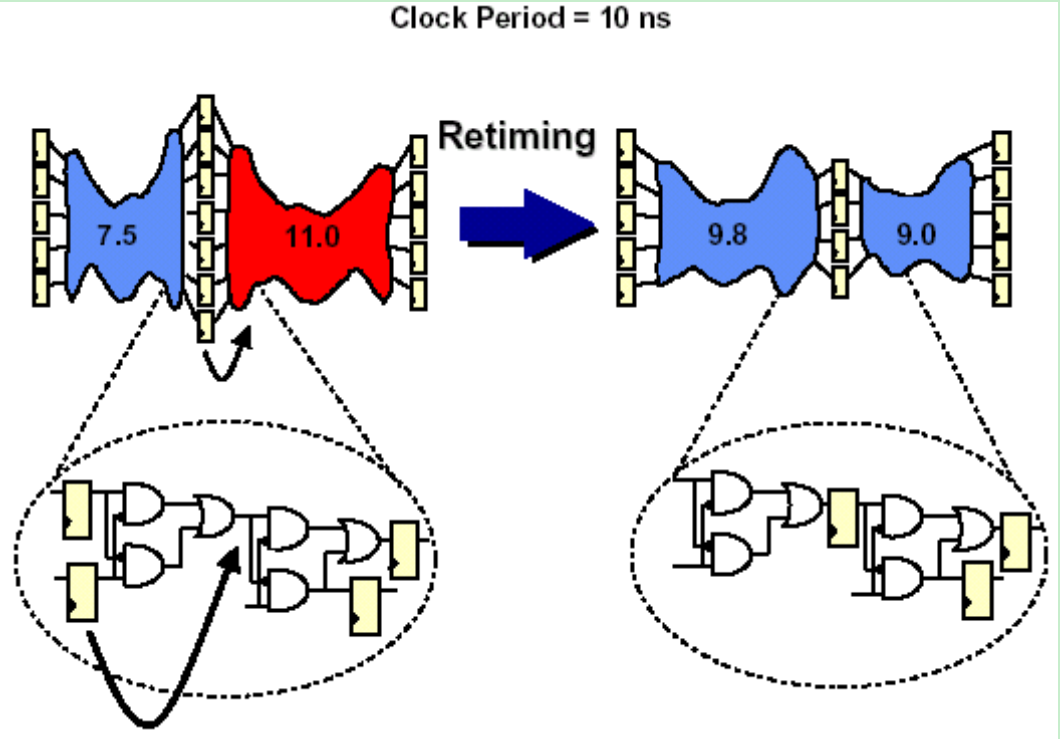

首先是Retiming:

如上图所示,当系统设计目标为时钟周期为10ns时,左边的电路显然不符合要求了,因为其最大路径延时为11ns,已经大于了10ns,这就导致了时序不闭合,未能达成设计目标。不过目前的FPGA IDE都支持Retiming技术,通过Retiming技术,可以均衡各个模块之间关系,重新调整,以降低最大路经延时。显然,Retiming技术会改变原有的设计,也可能会带来一些潜在的时序问题(甚至是逻辑问题,毕竟IDE还没有那么聪明)。所以,对于初学者来说,不要盲目地使用Retiming技术,必须在完全了解设计的情况下,按照一定和规范和步骤使用(每一个FPGA厂商的IDE都有相关的文档告知设计者要遵循什么样的过程的)。

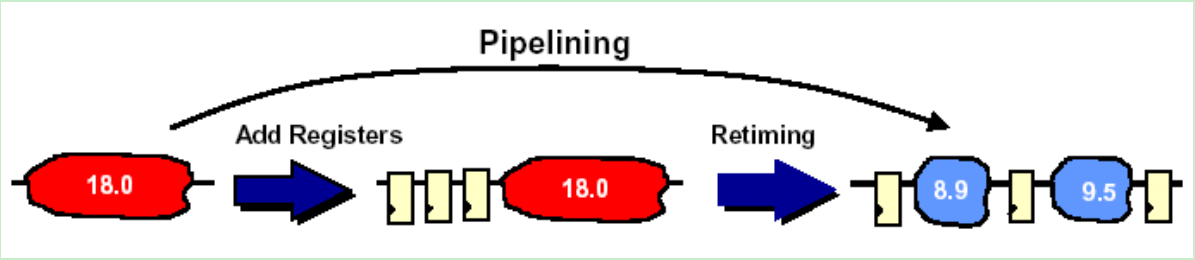

流水线技术(Pipeling)也不是什么新玩意了,说其是一种技术,还不如说是一种思想。关于流水线设计思想,网上已经有很多人介绍过了,这里就不详细说了,只来聊一聊时序优化方法中的流水线技术。

如上图所示,对于那些特别复杂的组合逻辑,可以通过向其中插入一些寄存器来打破长逻辑,以降低最大的Clock-to-Setup的路径延时,使得设计达到预期的设计目标。