静态时序分析之——如何计算时序参数

1赞静态时序相关博文连载目录篇:http://blog.chinaaet.com/justlxy/p/5100052092

这一篇文章将通过一个简单的例子来介绍一下如何计算时序参数(Timing Requirements)。

在介绍例子之前,先讲一些基本的东西:一般情况下,在FPGA的设计过程中有三种类型的速度要求。分别是运行速度要求(Timing requirement)、数据传输速率要求(Throughput)以及数据潜伏期(Latency,很多人把他简单的翻译为延时,其实是不恰当的,因为Latency是和Delay有区别的)。

简单的来说,Timing Requirement就是你的设计能跑多快,能够在多高的频率下运行,单位是Hz;Throughout就是平均的数据传输速率,单位是Bps;Latency就是从有效输入数据出现到有效输出数据出现之间的时间(就好比你在按下手机拨号键之后,对方花了多长的时间之后手机上开始响铃,当然,这是一个不太恰当的例子……不过能说明问题就好)。

不知道大家有没有注意过,市面上的ADC(模数转换器)有这样一个现象:精度高的一般转换时间较长,采样速度也低;而精度低一点的,一般转换时间都要短一点,采样速度可以做的比较高。有兴趣的可以去ADI的网站上了解一下,其高速ADC的采样位宽一般是12-16bits,而低速ADC采样位宽有的则高达24bits!!

ADI官网:http://www.analog.com/cn/products/

这是因为,在高速ADC的设计中,普遍采用了流水线技术(Pipelining),但是与此同时,却增加了器件的Latency(从ADC的参数上来看,就是转换时间),同时也限制了采样精度的提高。

在FPGA设计过程中,也是同样的道理,高的Throughout往往意味着要采用更多的Pipeling,同时也带来更多的Latency。而较低的Latency则需要更多的组合路径(Combination Paths),同时将会导致Throughout和时钟频率的降低。

接下来回到正题,也就是这篇博文的标题内容,以一个简单的例子,分析一下如何计算Timing Requirement:

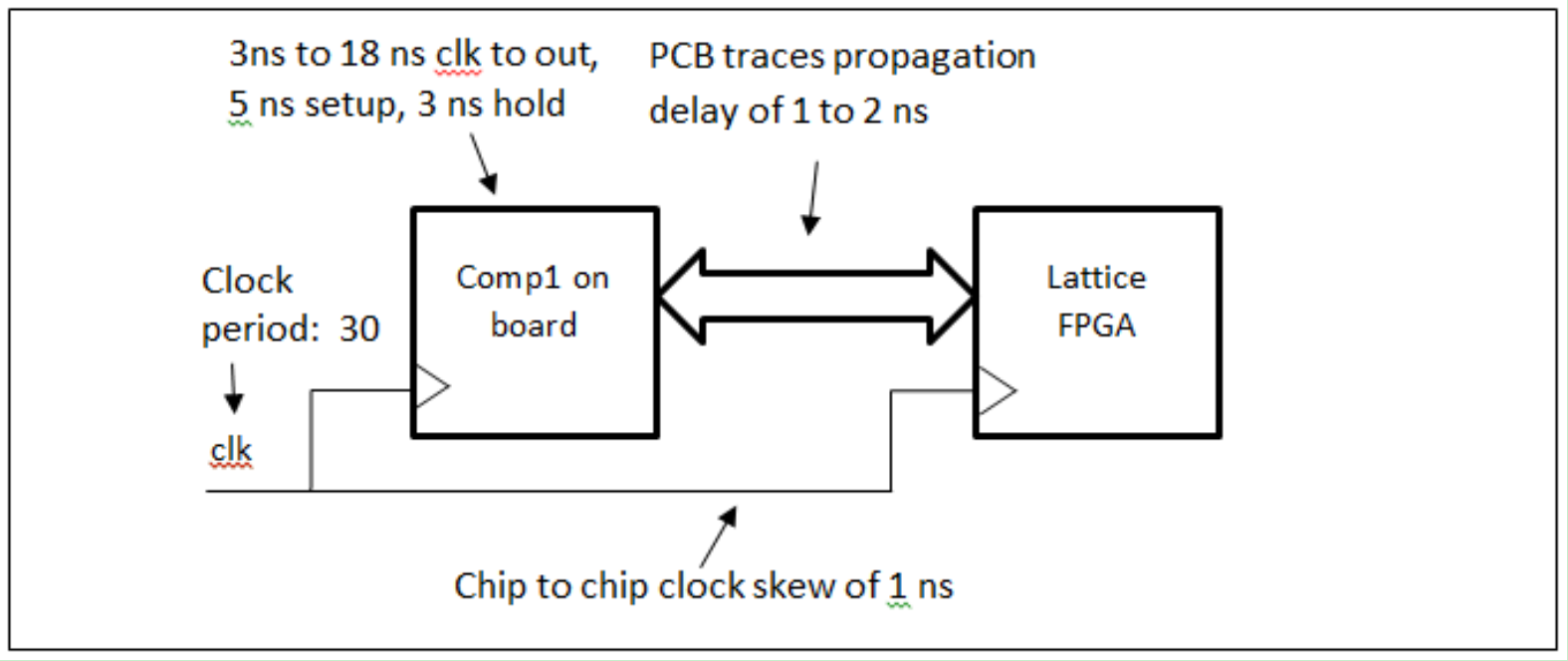

如上图所示,根据图中的信息,我们知道:

|-系统时钟周期:P=30ns

|-组件1(Comp1):

|-最大输出传播(propagation)延时(Tco):PDMAXp=18ns

|-最小输出传播延时(Tco):PDMINp=3ns

|-组件1输入建立时间:TSp=5ns

|-组件1输入保持时间:THp=3ns

|-最大板级传播延时:PDMAXb=2ns

|-最小板级传播延时:PDMINb=1ns

|-时钟差(Clock Skew):时钟到达FPGA的1ns之后到达组件1(不要在意图中线的长度,哈哈哈)

|-组件1到FPGA的时钟差:Tskew=1ns

根据上面的信息,我们可以计算出FPGA的相关时序参数(Timing Requirement for FPGA),同时给出具体的约束语句写法(以Lattice Preference Language为例):

|-时钟周期 P=30ns,或者频率为33.33MHz

|-FREQUENCY PORT "clk" 33.33MHz

|-输入建立时间(Input Setup)=P-PDMAXp-PDMAXb-Tskew = 30 - 18 - 2 - 1 = 9ns

|-INPUT_SETUP ALLPORTS 9ns CLKPORT "clk"

|-输入保持时间(Input Hold)= PDMINp + PDMINb + Tskew = 3 + 1 + 1 = 5ns

|-INPUT ALLPORTS SETUP 9ns HOLD 3ns CLKPORT "clk"

|-输出最大传播延时 = P - TSp - PDMAXb + Tskew = 30 - 5 - 2 + 1 = 24ns

|-CLOCK_TO_OUT ALLPORTS 24ns CLKPORT "clk"

|-输出最小传播延时 = THp - PDMINb + Tskew = 3 - 1 + 1 = 3ns

|-CLOCK_TO_OUT ALLPORTS MAX 24ns MIN 3ns CLKPORT "clk"