综合过程中的时序约束技巧(Synplify Pro篇)

0赞静态时序相关博文连载目录篇:http://blog.chinaaet.com/justlxy/p/5100052092

如题所示,这篇博文主要介绍一下综合过程中的一些时序约束技巧,具体的综合工具为Synplify Pro(LSE可能会在后面的博文介绍,可能……)。总的来说,Synplify Pro是一款功能非常强大的第三方综合工具,也是业界公认综合效率最高,最好用的综合工具,几乎所有的FPGA厂商都支持Synplify Pro。Lattice在其IDE Diamond中集成了Synplify Pro(For Lattice),当然用户也可以直接打开Synplify Pro进行综合等操作。本篇博文所讨论的内容都是在Diamond中进行操作的,不需要直接打开Synplify Pro进行操作。

首先,先来回顾一下之前博文中出现的那张图:

可以发现,综合过程中的时序约束主要来自于两个地方:SDC文件中和HDL源码中的约束。

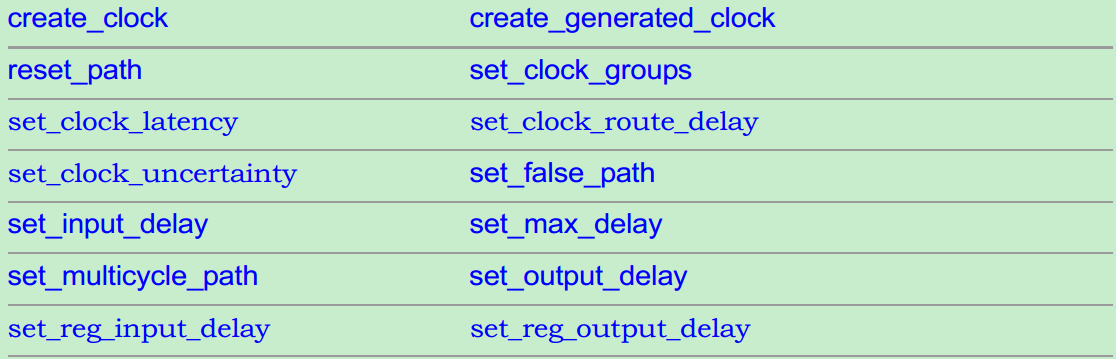

在Synplify Pro for Lattice Reference Manual的文档中,我们可以看到Synplify Pro支持以下这些时序约束:

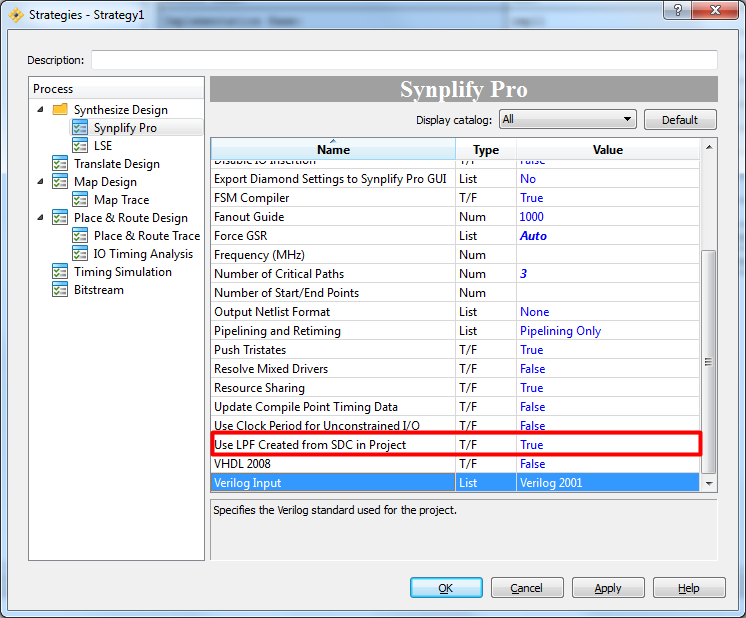

基本上囊括了,前面所介绍的大部分的时序约束要求。用户可以直接在HDL源码中使用这些约束,或者在SDC文件中写入这些约束。当综合过程完成后,Diamond会自动将相关的时序约束写入到LPF文件中,以供接下来MAP过程使用。当然,前提是Strategy相关的参数设置正确:Use LPF Created from SDC in Project = Ture,如下图所示:

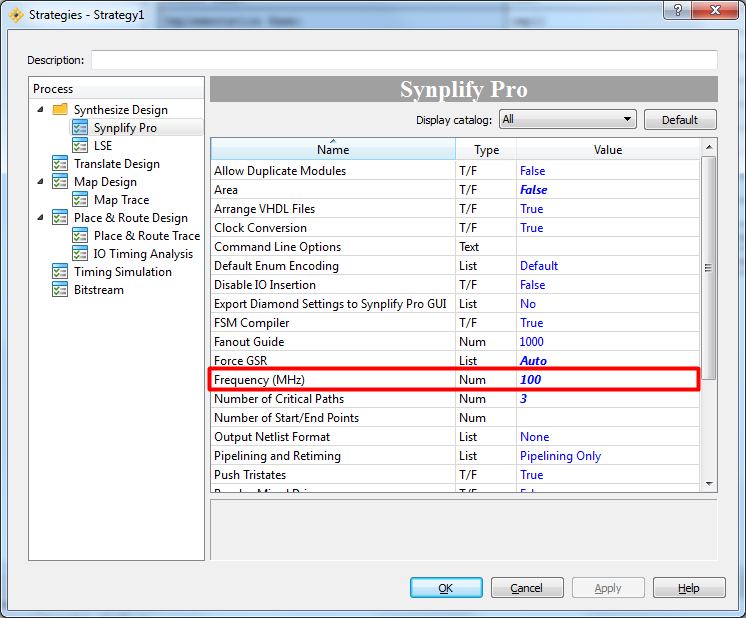

除此之外,还有一个大前提,就是必须将Strategy中的Area参数设置为False,否则综合工具会直接忽略SDC文件中的和HDL源码中的时序约束条件:

总的来说,综合过程中的时序约束比较简单,因为此过程更多的任务是查找出HDL设计中的逻辑错误或者不合理的地方。初学者可以在综合过程中只指定时钟时间(如下图,如果不指定的话,综合工具会尽力优化以到达设计的最大时钟频率),其他的约束条件都放在LPF文件中(或者通过SpreadSheet View中直接设置)。因为Synplify Pro虽然也可以进行静态时序分析,但是其分析的精度比较低,只能作为一个参考。因此,没有把过多的精力放在分析Synplify Pro产生的时序分析报告上。高手嘛,请随意……

此外,Strategy中还有很多的配置参数,有兴趣的可以自己去了解一下。

补充说明:这里说Synplify Pro时序分析的精度低主要原因有两个方面(并不是Synplify Pro本身的问题):

1、Synplify Pro时序分析的基本数据来自Lattice的器件库文件中的参数,因为Synplify Pro只是进行了综合(其实Synplify Pro本身是有MAP功能的,但是必须要单独的打开Synplify Pro进行操作),而MAP是接下来由Diamond完成的,所以Synplify Pro分析的时序模型可能和MAP之后的实际模型有一定的差别;

2、Synplify Pro并不能分析PAR之后的时序,这和之前说的MAP TRACE的精度比PAR TRACE的精度要低的道理是一样一样的!