Under-Constraining与Over-Constraining

0赞静态时序相关博文连载目录篇:http://blog.chinaaet.com/justlxy/p/5100052092

如题,这篇博文主要讨论的内容为Under-Constraining与Over-Constraining,即欠约束和过约束。

所谓欠约束,就是说当前的设计缺少足够且有效地时序约束。如果某个设计处于欠约束状态,那么有很多潜在的时序问题可能并不能在静态时序分析中被发现。但是这些潜在的时序问题却很有可能在产品测试甚至生产之后的被发现,这就会带来很大的损失和风险。

一般情况下,造成欠约束(Under-Constraining)主要有一下几种原因:

|-缺少时钟约束

|-跨时钟域的时钟未建立相位关系

|-未定义IO特性,或者IO特性定义不恰当

|-异步逻辑未使用MAXDELAY进行约束

|-内部产生的时钟或者潜在的时钟信号未得到有效约束

|-关键路径被禁止分析(Critical Paths Blocked)

为了确保每一个关键路径都得到了有效地约束,而没有处于欠约束的状态下,我们可以通过以下两种方式进行检查:

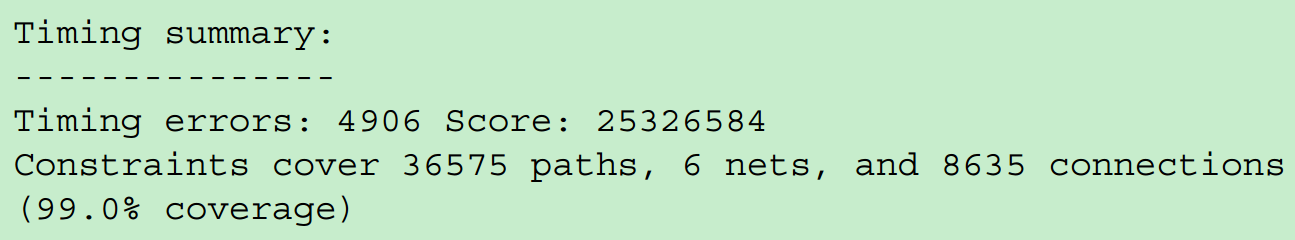

1、检查TRACE的报告的Timing summary部分,如下图所示:

这个例子中的约束覆盖率(coverage)是99%,一般来说,coverage至少要达到95%,才能保证当前设计不处于欠约束状态下。

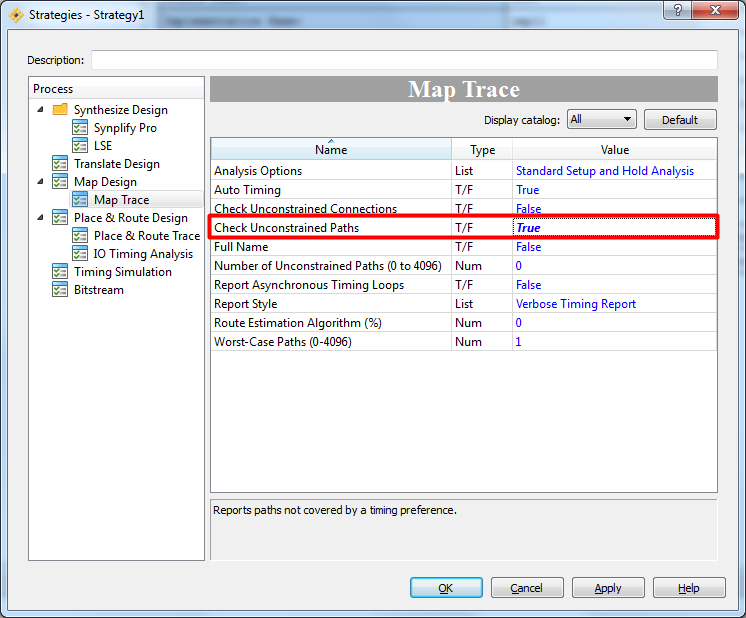

2、此外,我们还可以将MAP TRACE和PAR TRACE相关的Strategy设置,Check Unconstrained Paths设置为True。此时,TRACE的报告中便会出现一些关于未约束路径的信息:

应当注意,此时的会出现所有的未得到约束的路径,但是,实际情况下,某些路径确实不需要去约束(如common ground net)。

造成过约束(Over-Constraining)主要有一下几种原因:

|-未详细说明的多周期路径(Unspecified multi-cycle paths)

|-来自(或到)IO多周期路径有不同的约束

|-FREQUENCY/PERIOD设置得比实际需求值要高

一般情况下,使用实际需求的FREQUENCY/PERIOD值作为约束条件是一个很好的习惯和选择。但是也有的场合,需要将约束设置得高一点,以测试当前的设计的最高性能等参数。此时,设计者在设置时钟约束的时候,可以使用PAR_ADJ选项,以避免过约束带来的问题。

为什么要避免过约束呢?因为,过约束往往会使PAR的运行时间大幅提升,甚至PAR失败!进而导致我们的开发效率降低。因此,合理地使用时序约束,避免欠约束和过约束情况的发生,是一个掌握静态时序分析技能的一个基本要求。