ECP5/ECP5-5G SerDes硬件设计注意事项(一)

0赞Lattice ECP5/ECP5-5G SerDes系列文章,目录篇:http://blog.chinaaet.com/justlxy/p/5100064954

Lattice ECP5/ECP5-5G的SerDes和前几代产品ECP3/ECP2M/SCM有较大的差异,在硬件设计时,应当注意ECP5/ECP5-5G SerDes的硬件设计需求,不可以直接照搬之前ECP3的设计,或者其他厂商的相关设计。

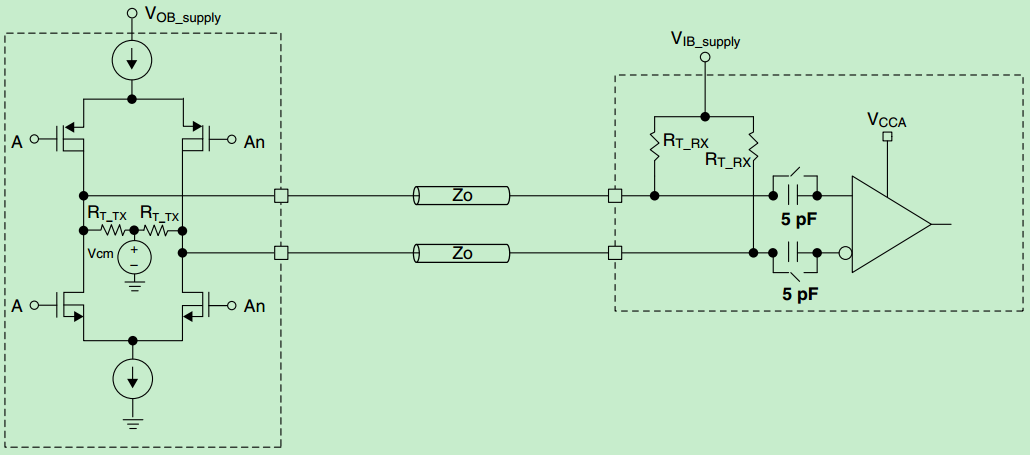

ECP3/ECP2M/SCM的SerDes集成了CML(Current Mode Logic)的输入输出Buffer,也就是说ECP3/ECP2M/SCM的SerDes输入输出接口都是CML的。但是ECP5/ECP5-5G的SerDes输入采用的是CML,而输出采用的是H桥结构的LVDS接口。ECP5/ECP5-5G的SerDes输入输出Buffer如下图所示:

ECP5/ECP5-5G的SerDes采用了低功耗设计,其功耗相比于ECP3等器件要低一些。ECP5的VOB/VIB电压(VCCHTX/VCCHRX)为1.1V,而ECP5-5G由于需要支持更高的速率,因此其VOB/VIB电压为1.2V。用于SerDes内部的混合信号电路供电的VCCA虽然和VOB/VIB的电压相同,但是其对电源的质量要求很高,一般建议将其与VOB/VIB电源区分开来,单独供电,比如用磁珠隔离(后面会详细地讲)。

注:需要特别注意的是,对于ECP5/ECP5-5G来说,每个DCU有两个Channel,每个Channel都有一个与之对应的VCCA。即使用户仅仅只使用了某个DCU里面的一个Channel,也需要同时对两个VCCA供电。对于不需要使用的Channel,用户可以不在逻辑中例化,或者例化后将其Power Off掉即可。

注:实际上,对于不使用的Channel,最好将所有的电源都供上,而不仅仅是VCCA。对于不使用的DCU则没有这个要求,但是仍然要求将不使用的DCU的VCCA接上。

注:对于同一个Channel,如果只是用Tx或者只是用Rx,还是建议同时对VOB和VIB供电,以抑制可能的噪声。

VCCA对电源要求很高,如果将不使用的Channel的电源引脚悬空的话,可能会带来噪声并作用到需要使用的Channel的VCCA上,进而导致SerDes工作异常。

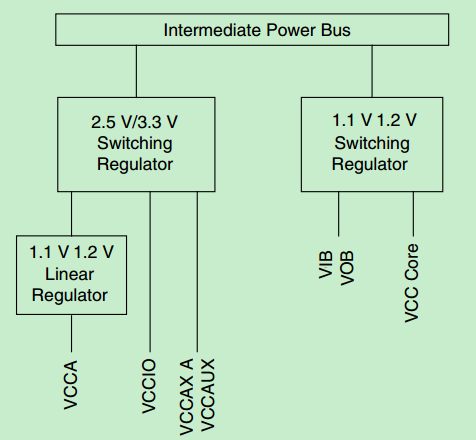

为了保证VCCA获得稳定,干净的电源,我们建议使用LDO来驱动VCCA。但是考虑到LDO的效率和负载能力,一般建议先使用DC-DC将输入源电压将至2.5V/1.8V,再使用LDO将其转换为VCCA所需要的1.1V/1.2V。如下图所示:

对于VIB/VOB和VCC Core而言,可以使用DC-DC,但是还是推荐使用LDO。因为如果VIB/VOB上面有很大的噪声的话,也会一定程度上对VCCA造成影响。

注:需要注意的是ECP5/ECP5-5G并没有独立的VCCPLL引脚,因为ECP5/ECP5-5G的内部通用PLL直接从VCC Core上面取电了(FPGA内部集成了相应的降噪电路)。如果VCC Core的电源不够干净的话,其带来的噪声会转嫁到PLL输出的时钟上,导致输出时钟的抖动变大。当然,对于绝大部分的应用来说,这种影响可以忽略,但是如果用户想用ECP5/ECP5-5G内部的通用PLL的输出时钟作为SerDes的参考时钟源的话,其带来的抖动可能导致SerDes内部的Tx PLL/Rx CDR失锁,甚至无法锁定!

当然,仅仅使用LDO还远远不够,用户最好使用无源滤波网络(Passive Filter Network)和磁珠将VCCA和其他电源网络完全隔离,Lattice推荐的处理方法如下(以ECP5-5G为例):

一般建议在VCCA管脚附近出放置多个电容,并串联一个性能合适的磁珠。一般建议在每一个VCCA附件放置22pF~1000pF,10nF,100nF,1uF和10~22uF电容各一个,其中10~22uF最好使用钽电容,其他电容使用普通陶瓷电容即可。磁珠型号可选用Lattice推荐的BLM41PG471SN1L,或者性能相似的型号。BLM41PG471SN1L的主要特性可参考如下链接:https://www.murata.com/zh-cn/products/productdetail?partno=BLM41PG471SN1%23

注:一般建议将同一个DCU的两个VCCA连接到一起,不建议分开处理。如果用户坚持要将两个VCCA分开处理,并且均分别使用了磁珠隔离,那个相应的电容数量也需要增加,即每个VCCA需要一组上述的电容。这是因为,磁珠会将两个VCCA隔离成两个电源块,如果其中的一个Channel处理不当,其带来的噪声会反作用到该Channel的VCCA上,如果没有足够的电容,则会导致相邻的VCCA供电异常。举个例子,如果用户同时使用了一个DCU内的两个Channel,其中的一个Channel突然被拔掉,会导致该Channel的CDR失锁;于是CDR会立即尝试去重新锁定,则会导致该Channel的电源功率需求瞬间增加,但是由于磁珠的隔离作用,LDO并不能立即响应该Channel的功率需求。这种情况下,可能会导致相邻的VCCA供电异常。但是,如果该Channel的VCCA附近有容值较大的电容,该电容的存储的电量可以弥补该Channel的VCCA瞬间的功率需求,以解决磁珠导致的LDO输出功率响应滞后的问题。

注:用户可以参考Lattice官网上的ECP5/ECP5-5G Versa板上的SerDes电源接法。

虽然VCCA来自LDO,而LDO本身一般也不会引入较大的噪声,但是如果LDO的输入已经存在较大的噪声的话,LDO是无法抑制这些噪声的。DC-DC虽然相比于LDO有很高的功率转换效率(尤其是在输出远小于输入的情况下),但是其往往会引入较大的噪声,其中主要是DC-DC的开关噪声。

对于陶瓷电容来说,其自感系数(感应系数,Inductance)往往与其容值有直接的对应关系。因此退耦电容(Decoupling Capacitor)对应的频率带宽一般都比较窄,不同的容值匹配不同频率的电源噪声。因此,在没有准确地确认系统中所有可能存在的电源噪声(这往往也不太现实)的情况下,使用多个不同的容值的电容并联,还是非常有必要的。

注:退耦电容的有效频率带宽往往是由等效串联电阻(ESR)和其Q值(Quality Factor)共同决定的。

不同于陶瓷电容,钽电容由于其特殊的特性,往往拥有更宽的有效带宽,因此Lattice强烈建议在无源滤波网络中的10~22uF电容使用钽电容。但是相比于普通的陶瓷电容,钽电容往往体积更大,价格更高。

注:用户可以参考Lattice网站上的TN1033,High-Speed PCB Design Consideration文档,以获取更多的关于电容容值、封装和类型选取,以及PCB Layout需要注意的事项。

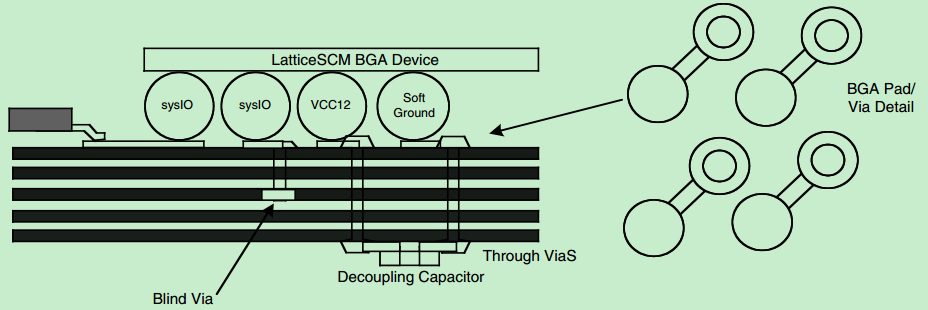

Lattice建议将电容放置在FPGA芯片的背面,如下图所示: