静态时序分析的基本流程(Lattice Diamond篇)

0赞静态时序相关博文连载目录篇:http://blog.chinaaet.com/justlxy/p/5100052092

如题,这篇博文来简单地聊一聊使用Lattice的IDE Diamond进行静态时序分析的一般步骤。

Step1:编写高效的HDL的源码

说道如何使FPGA设计达到时序闭合(Timing Closure)工程师最容易想到的方法就是通过进行综合约束、布局布线约束、和其他的优化技术提升系统性能,当然这些都是设计过程中所必需的,但所有这些优化方法对于系统性能的提升都是有限的,系统的性能最终还是取决于工程师的设计( coding style),其中同步设计是最重要的一点。具体的大家可以去看一下一个叫作“HDL Coding Guidelines”的文档,该文档,可以直接在Diamond的Start page中找到,如下图所示:

Step2:使用合适有效的时序约束

“有效的时序约束”,这是我们之前的几篇博文所一直讨论的问题。实际上,时序约束不仅仅是对于静态时序分析而言的,它是贯穿整个FPGA设计流程中的,包括综合(Synthesis)、MAP和PAR。这里为什么说“使用”,而不是说“编写”呢?是因为,时序约束除了可以像我们之前那样介绍的一样通过在LPF文件或者HDL源码中(或者在SDC文件中)直接编写之外,还可以通过Diamond的集成工具SpreadSheet View进行GUI式的设置。其中,在HDL源码中和在SDC文件中的时序约束会影响到综合工具的操作,以及后面的MAP和PAR的操作。而在LPF文件中的时序约束(包括通过SpreadSheet View进行设置的,实际上,最终也是写入到LPF文件中的),可能不会影响到综合过程(LSE和Synplify Pro对此处理方式不同)。

当然,除此之外,还有一个可以修改时序约束的工具——Timing Analysis View。该工具的具体用法,会在后面详细聊……

Step3:尝试性的运行MAP、MAP TRACE、PAR、PAR TRACE等操作

此过程主要用于检查HDL的设计中的一些错误和不合理的地方。这里有一个黄金法则(Rule of Thumb):在设计前期尽量先用MAP TRACE来检查时序问题,因此此时主要的问题都存在与HDL的设计上。当MAP TRACE基本上没有什么问题的时候,在使用PAR和PAR TRACE进行时序分析,并充分利用Timing Analysis View工具,以节省开发时间(相对于MAP,PAR会花费大量的时间)。

Step4:认真分析Report

认真分析MAP report、MAP TRACE report、PAR report、PAR TRACE report以及PAD report。根据report中的相关信息,调整HDL设计或者时序约束条件……

Step5:如果需要,添加或者修改约束条件

如果当前约束不合适,可以通过修改一级、二级时钟分配(Primary and secondary clock)、调整和PLL相关的IO时序,将关键路径(Critical Paths)的相关组件进行组合(Group)等……

Step6:检查关键路径、高扇出网络和长组合路径

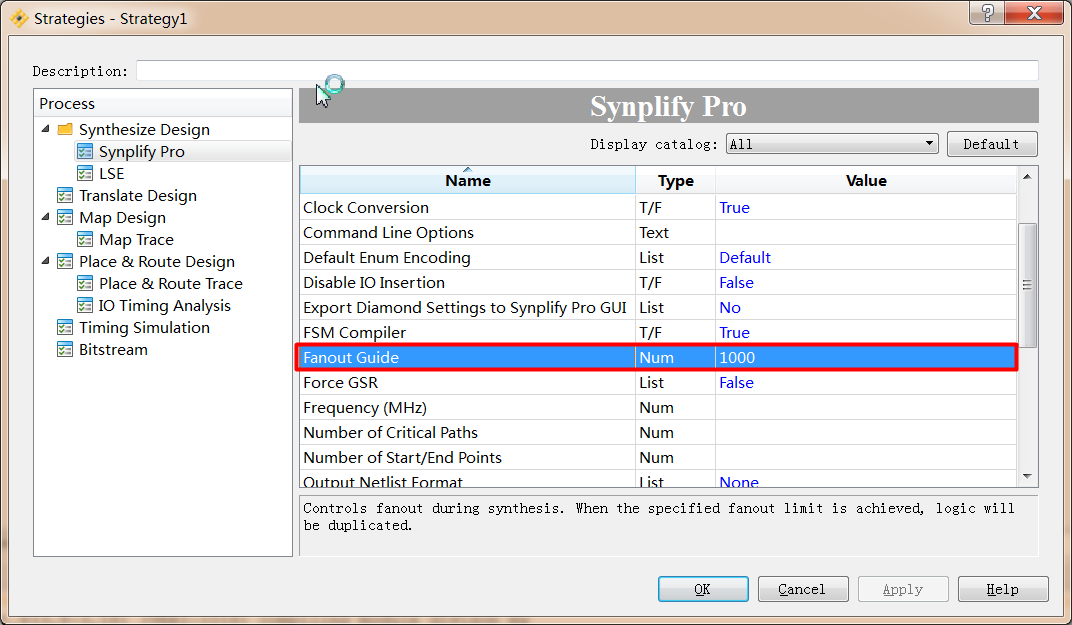

对于高扇出(High-fanout)网络,可以使用时钟(复位)网络资源(对于时钟和复位信号来说),或者插入冗余资源来降低扇出。当然这个不需要设计者去做,我们只需要在Strategy中进行相应的设置就可以,如下图所示,可以根据实际需求适当提高或者降低最大扇出。

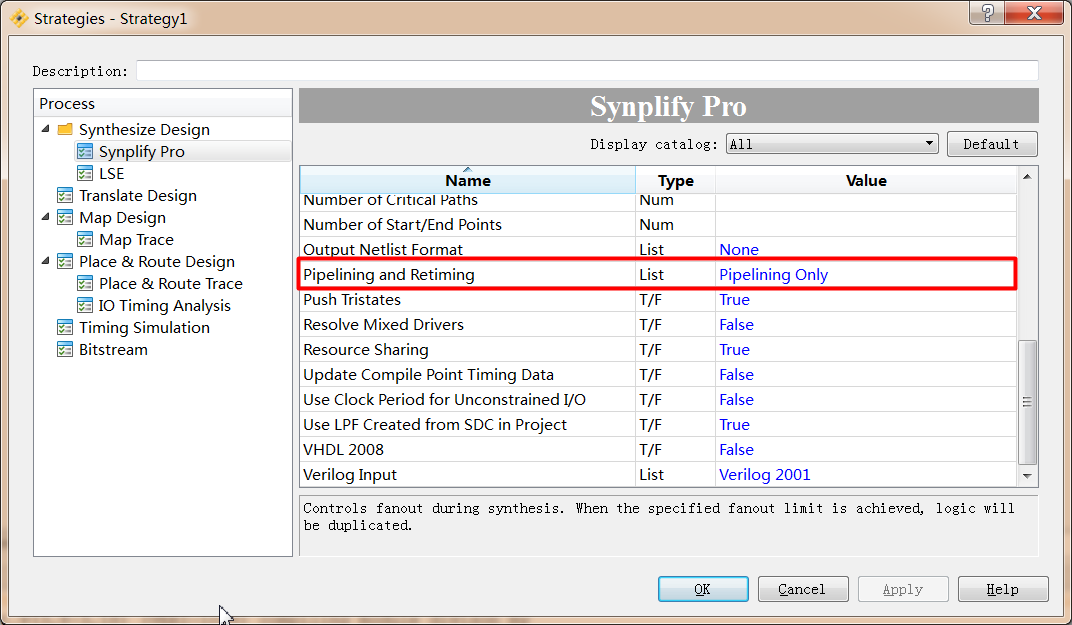

对于长组合路径,可以采用之前介绍的Retiming或者Pipeling技术。具体地来说,用户可以修改HDL源码,将原设计修改为流水线设计;也可以通过Strategy进行设置,引导相关工具自动采用Retiming和Pipeling技术,如下图所示:

Step7:如果需要,可以通过Floorplanning进行一些layout的调整

如果通过以上6个步骤反复迭代,仍然不能到达预期的时序目标时,可以考虑使用Floorplanning工具适当调整Layout。如,将一些时序要求严格的组件(模块)放置在一起,以缩短走线距离……