ECP5/ECP5-5G SerDes硬件设计注意事项(二)

0赞Lattice ECP5/ECP5-5G SerDes系列文章,目录篇:http://blog.chinaaet.com/justlxy/p/5100064954

上面一篇文章讲到,SerDes的VCCA对电源的质量要求非常高,用户应当尽可能的避免供给VCCA的电源存在较大的噪声。然而,除了这一点,用户还需要考虑来自PCB上的其他噪声源,比如VCCA走线附近的噪声源,甚至是FPGA内部的噪声源。本文将继续介绍,如何尽量避免引入噪声源,并尽可能地抑制它们。

ECP5/ECP5-5G SerDes支持100~1300mV可以配置的输出差分摆幅,在特定情况下,更高的输出差分摆幅往往可以提高SerDes信号的抗干扰能力。但是这并不意味着,提高输出差分摆幅一定是有益的;提高差分摆幅往往会导致更高的功率消耗,并对信号压摆率和Rx CDR的性能提出了更高的要求。

用户首先要考虑的是,如何将可能存在的噪声隔离,然后才是考虑SerDes本身的抗干扰设计。比如,用户需要将信号线(尤其是单端信号)远离VCCA的走线,尽量不要使用SerDes相邻的Bank的IO作为单端信号等等。Lattice建议VCCA的走线尽可能的粗,电源回路尽可能的干净,远离干扰源。因此,VCCA的走线是第一优先级,然后是其他的电源线,然后是SerDes的信号线/参考时钟线,然后是其他的差分线,最后是单端信号线。

注:单端信号,尤其是频率高的,压摆率高的单端信号,往往是数字系统中非常大的噪声源。用户应当将这些信号的走线远离那些对噪声比较敏感的元件和相应的走线。一般来说,单端信号的摆幅越大,压摆率越高,电压越高,驱动能力越强,频率越高;其所造成的噪声越大。这种噪声,对于数字系统本身可能影响不是很大,但是对于模拟系统的影响却有可能是致命的!

考虑到ECP5/ECP5-5G FPGA的SerDes是一种数模混合设计,为了避免给SerDes的模拟部分带来干扰,用户应该尽可能的避免使用SerDes相邻的Bank(Bank 8 & Bank4)作为单端IO使用。如果一定要使用,建议时钟这些单端IO作为一些控制信号或者状态信号,并尽可能的降低摆幅,压摆率,驱动能力和变化频率等,其对应的负载最好是容性负载(可以在单端信号线与地之间加一个10nF的电容),以抑制噪声的产生。

注:如果可能的话,尽量不要使用VCCA管脚相邻的IO,信号线的走线层尽量不要与VCCA电源层相邻。

ECP5/ECP5-5G SerDes同时支持交流耦合(AC Coupling)和直流耦合(DC Coupling),并且在SerDes CML 输入Buffer内部还集成了交流耦合电容,用户可以通过配置的方式使能或者旁路该电容。如下图所示:

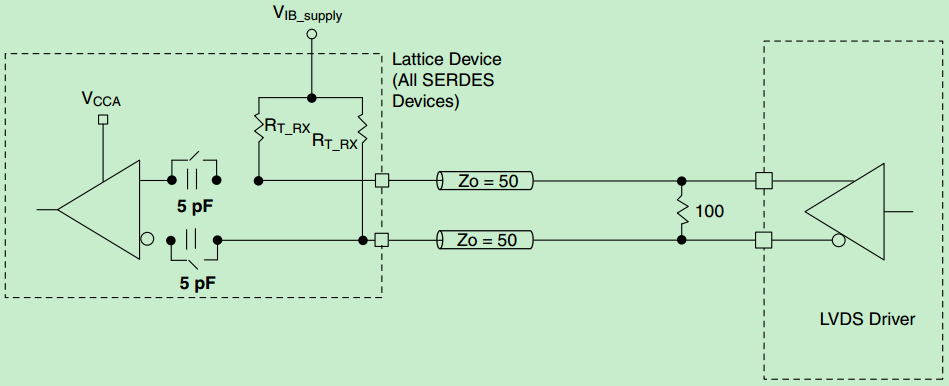

Lattice强烈建议,不管用户在外部使用的是交流耦合还是直流耦合,都尽量使能SerDes内部的5pF电容。因为该电容配合VIB的上拉左右,可以将输入信号电平拉倒适合采样的位置。当然是用内部5pF电容也是有条件的,如果用户的设计并没有是用直流均衡的编码(如8b/10b等),SerDes的速率太低(低于500Mbps)或者连续0/连续1过长(超过8~10个);用户必须将该5pF电容旁路。

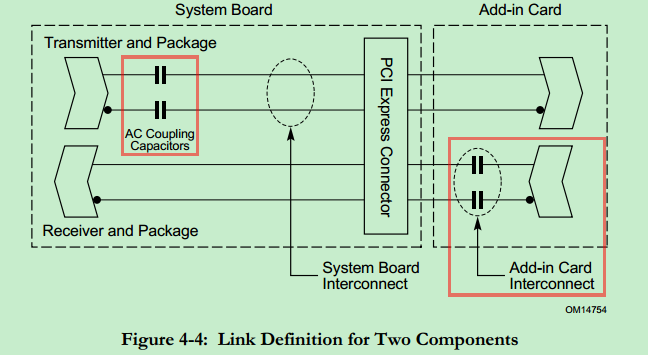

如果用户在外部使用的直流耦合,需要注意信号在接收端时,其电压范围是否超出了接收端器件定义的范围。如果用户在外部使用的是交流耦合,首先要保证使用了直流均衡的编码,且SerDes速度大于500Mbps;该电容应当放置于靠近发送端的位置,以PCIe Card为例,如下图所示:

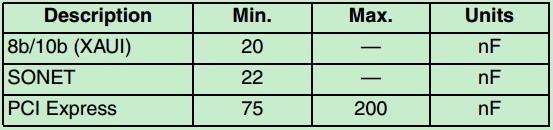

外部交流耦合电容的容值一般没有明确的要求,但是部分串行协议定义了该电容容值的范围,如下表所示。用户可以参考相应的频率,选择合适自己设计的容值。

注:建议尽量同时外部交流耦合和内部交流耦合电容,并使用直流均衡的编码。除非需要严格限制SerDes的速率在500Mbps以下。

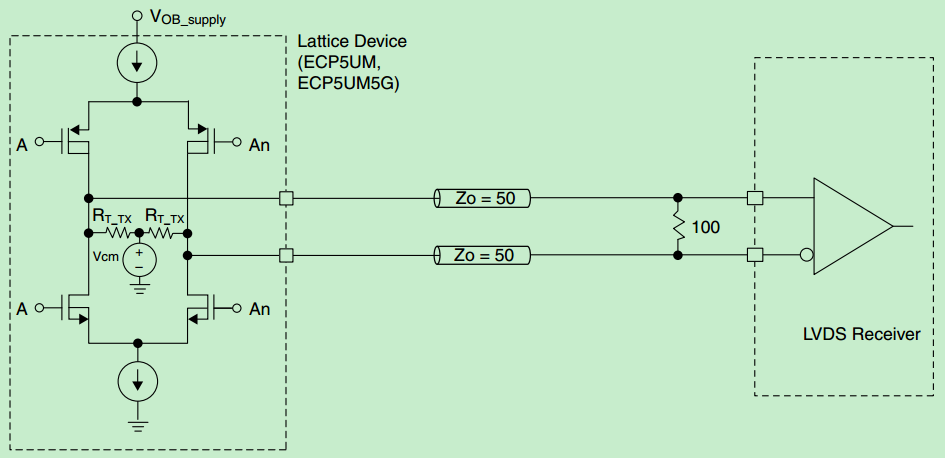

前一篇文章介绍道,ECP5/ECP5-5G的SerDes发送Buffer是LVDS接口的,只有输入Buffer是基于CML的。用户可以参考一下的接法,处理ECP5/ECP5-5G SerDes与标准LVDS接口的器件连接。首先是直流耦合的方式:

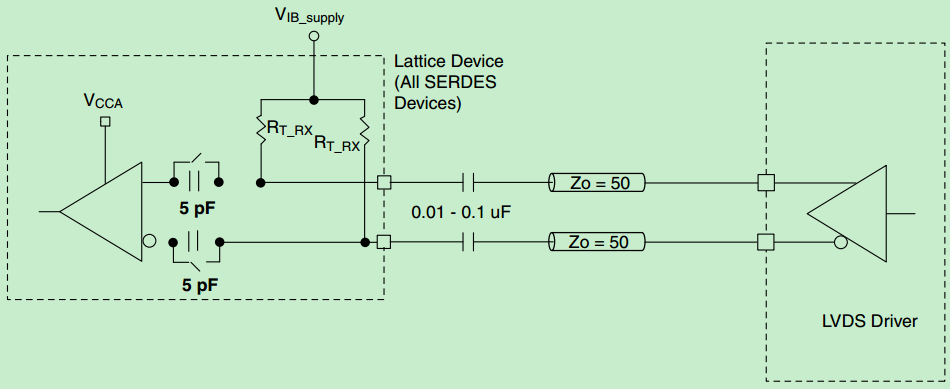

对于交流耦合,为:

关于与LVPECL和标准PCIe设备的连接,用户可以参考FPGA-TN-02077,Electrical Recommendations for Lattice SerDes。

ECP5/ECP5-5G的SerDes对参考时钟的要求很高,Lattice强烈不推荐使用来自Fabric的时钟源作为SerDes的参考失踪,即使是走PCLK/ECLK的时钟。一方面是用户一般很难保证该时钟的源是足够的稳定(抖动满足要求),另一方面是来自Fabric的时钟,往往会受到FPGA其他数字逻辑的干扰。

ECP5/ECP5-5G的参考时钟主要是用于TxPLL,同时也用于RxCDR的锁定和失锁检测。如果参考时钟的质量存在问题,不仅会导致TxPLL失锁,也会导致RxCDR的失锁。如果TxPLL无法锁定,有99%的可能性是参考时钟的质量有问题。关于参考时钟的具体要求,用户可以参考ECP5/ECP5-5G的Datasheet的3.24. SerDes External Reference Clock以获得更多信息。

注:ECP5/ECP5-5G SerDes TxPLL并不具备产生扩频时钟(SSC,Spread Spectrum Clocking)的能力,但是TxPLL和RxCDR都是可以兼容支持SSC的数据和参考时钟的。其支持的SSC范围是,30kHz~33kHz,0%~0.5%的扩频(Spreading)。如果用户使用了SSC,需要注意此时的数据Buffer的大小需求往往要比不支持SSC的时候要高一些。