ECP5/ECP5-5G SerDes基本特性介绍

0赞Lattice ECP5/ECP5-5G SerDes系列文章,目录篇:http://blog.chinaaet.com/justlxy/p/5100064954

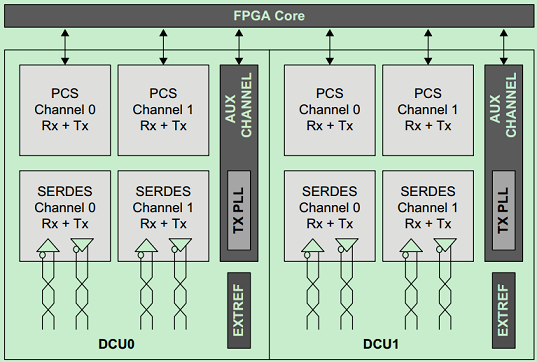

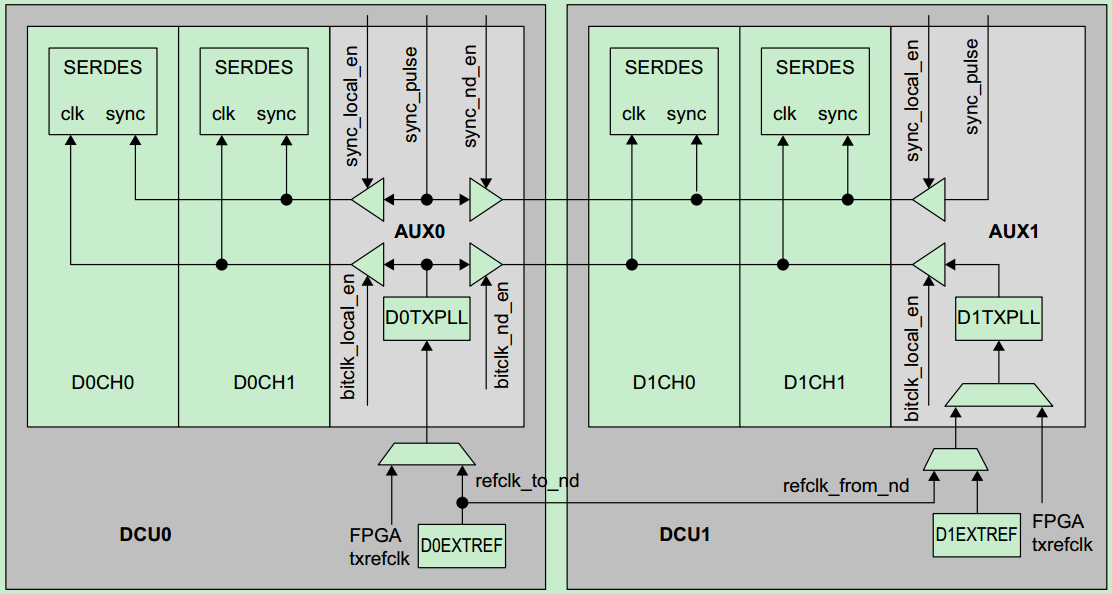

ECP5/ECP5-5G的SerDes和ECP3系列的SerDes结构上很像,但是相比于ECP3系列做了一些优化。ECP3采用的是65nm工艺,而ECP5则是40nm的工艺,因此ECP5 SerDes的功耗要相对较低。ECP3的SerDes以一个Quad为基本单位,每个Quad包含4个Channel,并公用一个AUX Channel。而ECP5的SerDes以DCU为基本单位,每个DCU包含2个Channel,并公用一个AUX Channel。这样做的好处是,同样是4个Channel,ECP5可以比ECP3同时支持更多的协议(不同的频率)。这是因为,每个AUX Channel中只有一个TxPLL,如果用户需要实现两种不同频率的应用,往往需要两个TxPLL。

注:如果是相同频率应用,是有可能在同一个DCU中实现的,但是也需要考虑SSC等因素。具体请参考TN1261,ECP5 and ECP5-5G SerDes/PCS Usage Guide。

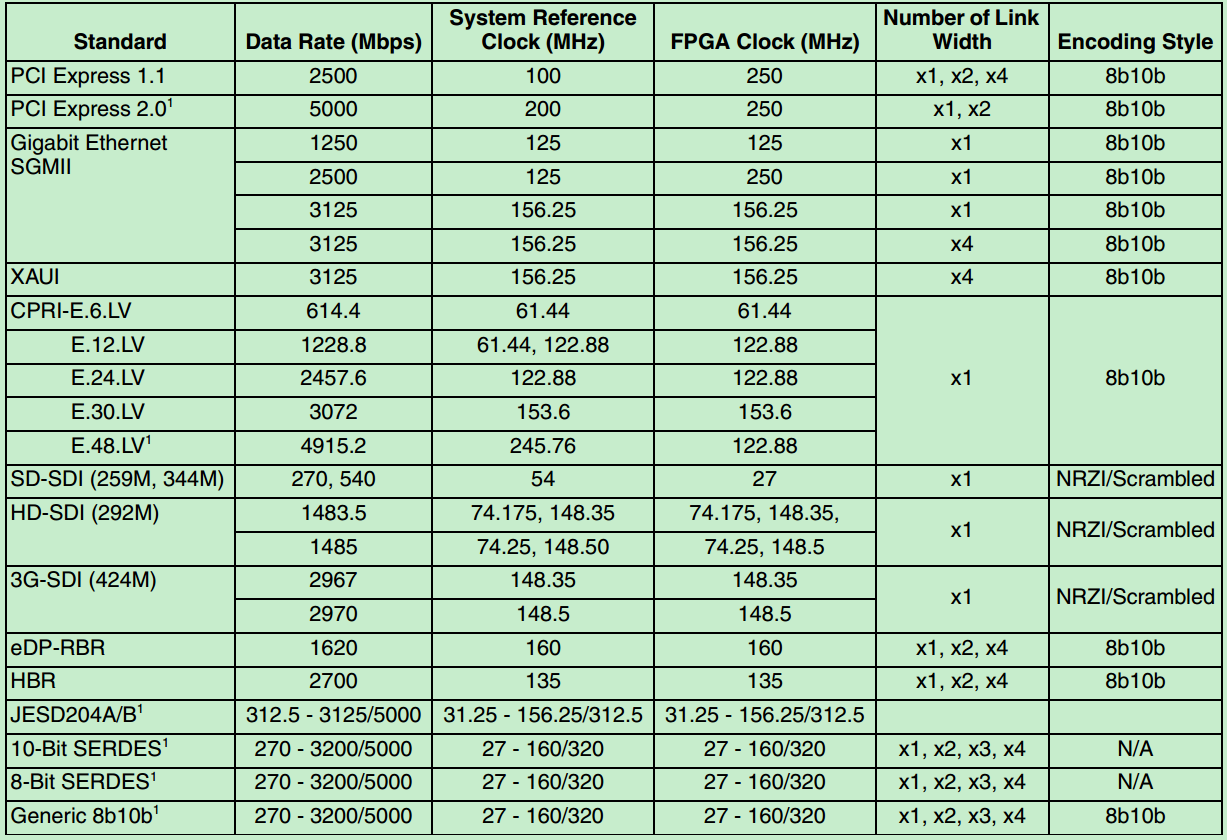

ECP5的SerDes支持270Mpbs~3.2Gbps的范围的速率,且在3.2Gbps的速率下,只有大约85mW的功耗。内部集成了8b/10b编解码器和CTC Buffer,支持多种串行协议:

注:EPC5-5G和ECP5几乎完全相同,只是其支持更高的速率,两者封装是完全兼容的。不过,需要注意的是,ECP5-5G的SerDes电压为1.2V,比ECP5的1.1V略高。

注:ECP5/ECP5-5G的Fabric实现250MHz Fmax的复杂逻辑比较困难,对于部分协议(其SerDes输出到Fabric的时钟,FPGA Clock大于200MHz的),建议使用FIFO将数据位宽加倍,并将时钟速率减半。

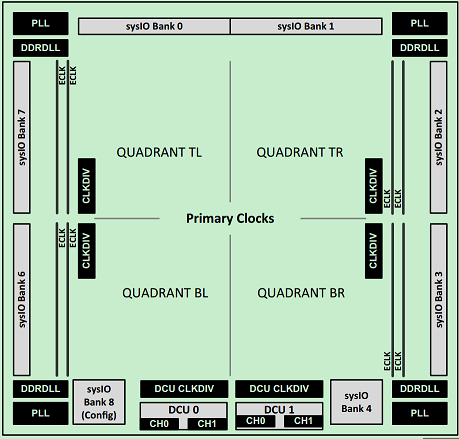

以ECP5/ECP5-5G-85系列为例,DCU在整个FPGA器件的位置如下图所示:

简化的DCU结构图如下图所示:

当用户需要同时使用4个Channel时,比如PCIe x4,XAUI x4等等,可以同时使用两个DCU,并公用DCU0的AUX Channel,如下图所示:

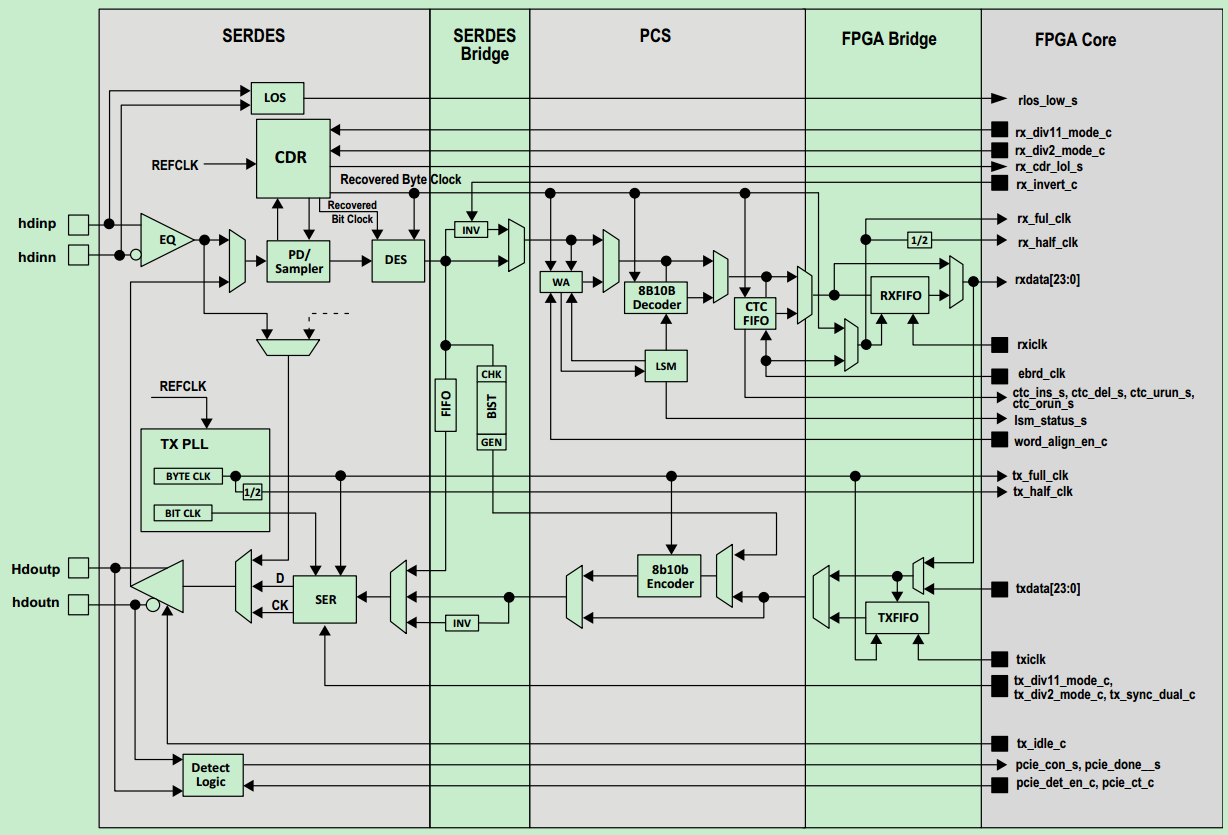

其中,Channel的详细结构图如下图所示:

注:其中TxPLL位于AUX Channel,而不是在每个数据Channel中,图中画出来只是便于用户理解SerDes中的时钟网络。