ECP5/ECP5-5G SerDes复位解读

0赞Lattice ECP5/ECP5-5G SerDes系列文章,目录篇:http://blog.chinaaet.com/justlxy/p/5100064954

这篇文章将详细地聊一聊ECP5/ECP5-5G SerDes的复位结构,以及需要的注意事项。考虑到SerDes/PCS是整个FPGA中最为复杂的数模混合设计,其对上电/复位顺序有着严格的要求。为了方便用户快速使用SerDes,而不用过多的去研究分析这些复杂的复位顺序,Lattice提供了相关的复位参考逻辑,用户可以在使用Clarity配置SerDes/PCS的时候选择自动生成该逻辑代码。

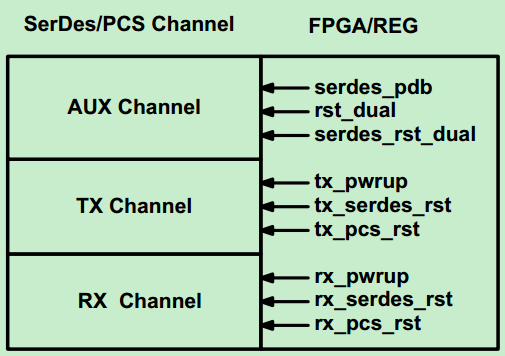

如下图所示,每一个DCU都有相对独立的复位/电源控制信号来分别控制各个Channel(包括各个数据Channel的Rx和Tx,以及AUX Channel)的电源使能、SerDes层复位、PCS层复位,以及针对整个DCU的复位和针对整个DCU SerDes层的复位。

其中,serdes_pdb为异步信号,低电平有效;当该信号有效时,整个整个SerDes/PCS(包括整个DCU内的Tx/Rx Channel和AUX Channel)都将处于Power Down的状态;

tx_pwrup为高电平有效,其主要对应的是串行发送器和LVDS Tx驱动器的电源。需要注意的是,当该信号由无效重新变为有效时,需要用户重新复位和Tx Channel相关的复位信号;

rx_pwrup也是高电平有效,其主要对应的是RxCDR,输入CML Buffer(包括均衡器和放大器)以及Loss-of-Signal检测器等。同样,当该信号由无效重新变为有效时,也需要用户重新护卫和Rx Channel相关的复位信号。

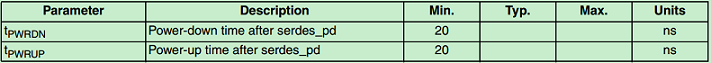

Power-Down和Power-up的生效时间如下所示:

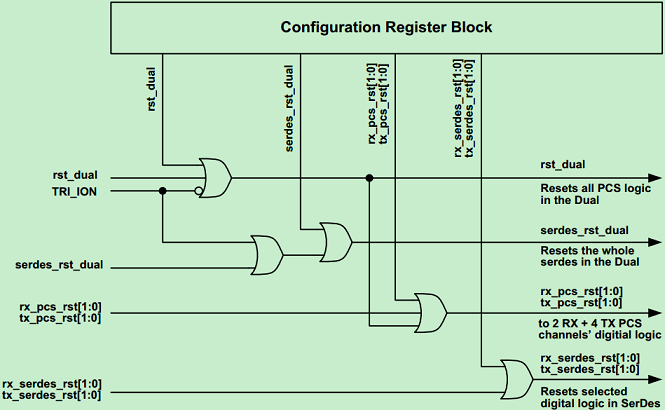

关于各个复位信号的层级关系,如下图所示:

注:用户除了可以直接通过这些复位信号去复位相应的模块,还可以通过SCI接口访问与这些复位信号对应的寄存器的相应bit来复位与之对应的模块。往寄存器中写“1”则表示复位,往寄存器中写“0”则表示释放复位。

各个复位信号的详细作用范围,如下表所示:

上面提到,ECP5/ECP5-5G的复位顺序较为复杂,一般不建议用户自己去实现顺序复位逻辑,用户可以在配置SerDes/PCS的时候,选择使能Reset Sequence,此时Clarity会自动生成相应的顺序复位逻辑。该逻辑位于*_softlogic.v中,用户可以打开该文件并查看源码。Clarity配置如下图所示:

注:关于具体的复位次序要求,感兴趣的可以自行查阅TN1261,ECP5 and ECP5-5G SerDes/PCS Usage Guide。

Clarity自动生成的复位顺序逻辑(Reset Sequence Logic,RSL)的结构图如下图所示:

注:Diamond3.10/3.11产生的复位顺序逻辑似乎有些问题,建议用户尽量使用Diamond3.9产生的复位顺序逻辑。或者在用户自己的逻辑中为复位信号增加延时(主要针对的是上电复位情况),但是这种方式并非对所有协议都有效,所以尽量还是使用Diamond3.9产生的复位顺序逻辑。

如果是同时使用了两个Channel,尤其是两个Channel是分开例化的(甚至是两种不同的协议),这种情况略微复杂一点,具体请参考TN1261,ECP5 and ECP5-5G SerDes/PCS Usage Guide。